Xilinx Zynq RTL Firmware Code 짜보기

목차

- UART verilog Testbench 살펴보기

- UART Tx Verilog Module 살펴보기

- UART Rx Verilog Module 살펴보기

- APB Bus 살펴보기

- APB Register 설계하기

- Vivado UART 모듈 설정 하기

- Xilinx Zynq Firmware Code 짜보기(현재 포스팅)

이번 포스팅은 부록 같은 느낌으로 작성한다.

Xilinx Zynq RTL Firmware Code 짜보기

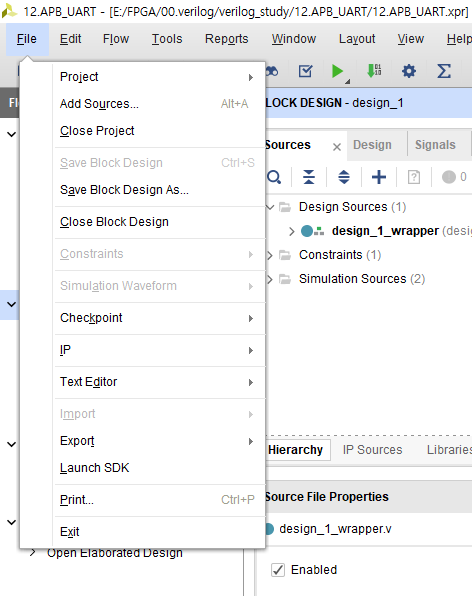

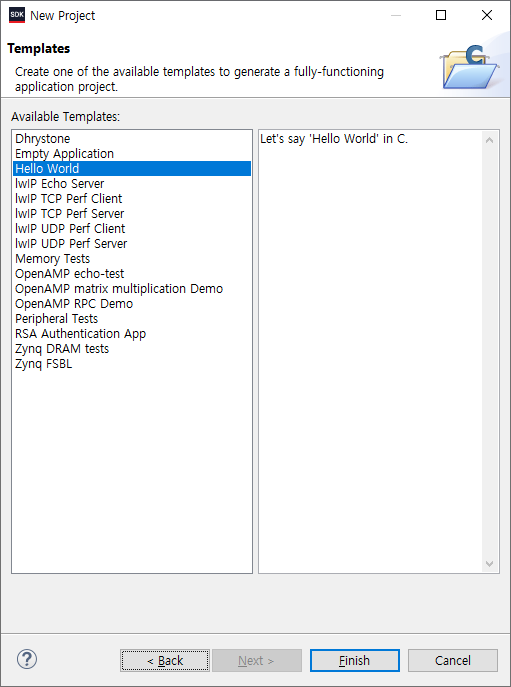

지난번 포스팅 화면에서 Launch SDK를 누르면 Xilinx SDK가 실행된다

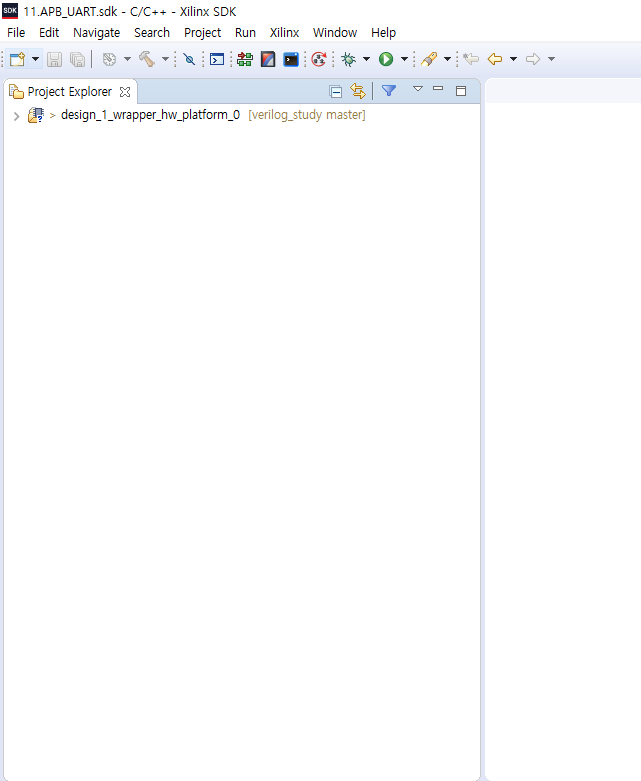

그러면 저런거 하나가 생긴다.

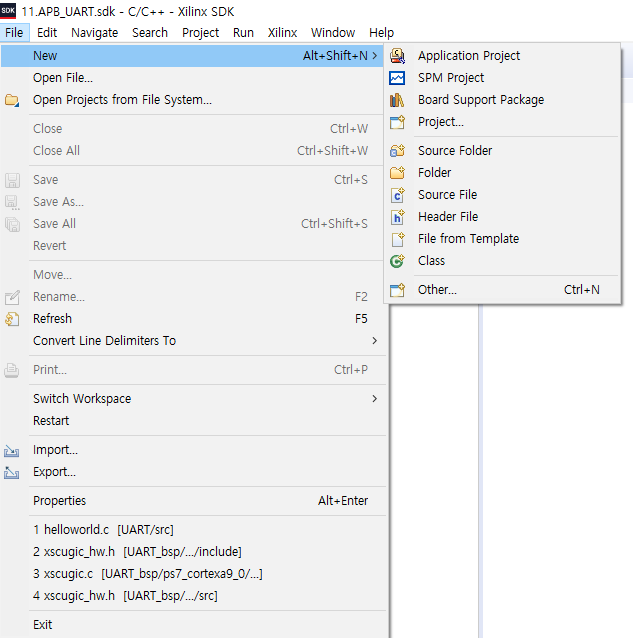

file – new – Application Project를 누른다.

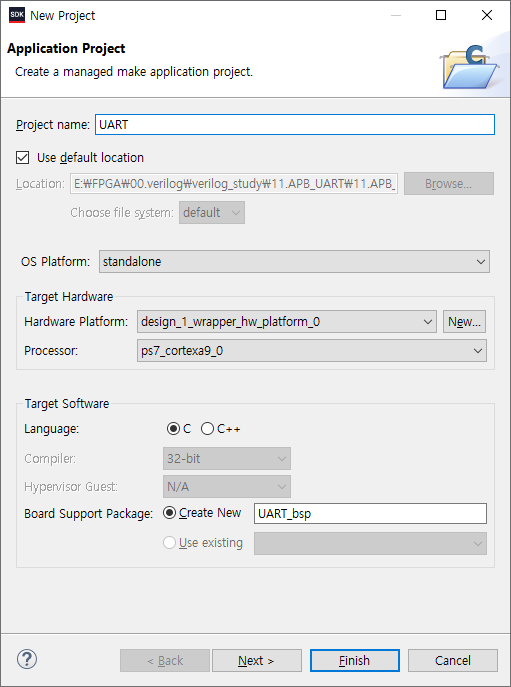

Project Name을 입력하고 넘어간다.

저러고 패스

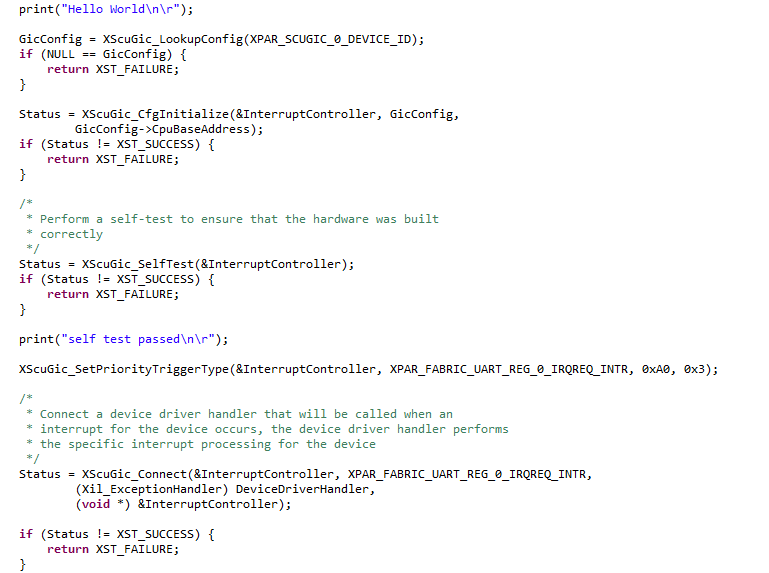

#include 추가하라.

#include "xparameters.h"

#include "xil_io.h"

#include "xscugic.h"인터럽트 컨트롤러를 추가해야한다.

XScuGic InterruptController; /* Instance of the Interrupt Controller */

static XScuGic_Config *GicConfig; /* The configuration parameters of the

controller */

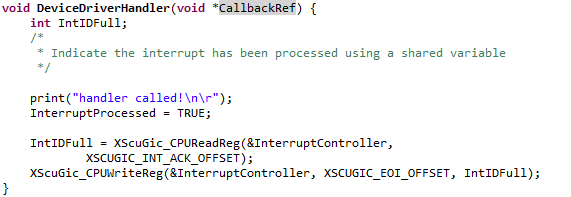

void DeviceDriverHandler(void *CallbackRef);

/*

* Create a shared variable to be used by the main thread of processing and

* the interrupt processing

*/

volatile int InterruptProcessed = FALSE;인터럽트 컨트롤러 설정을 해준다.

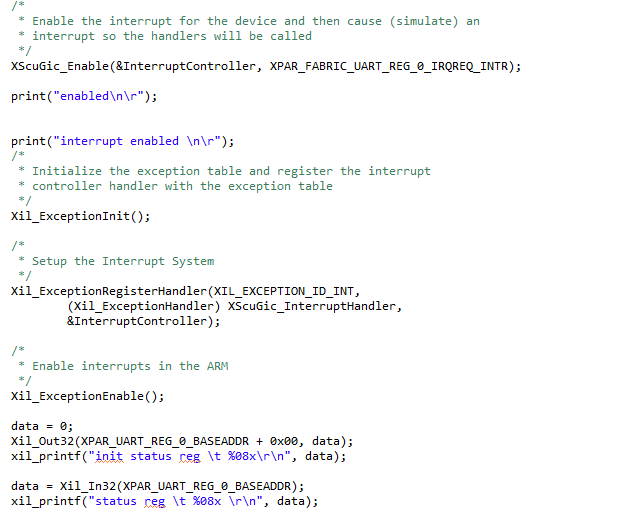

인터럽트를 활성화 한 뒤에, 설계한 RTL 모듈을 제어 한번 해본다.

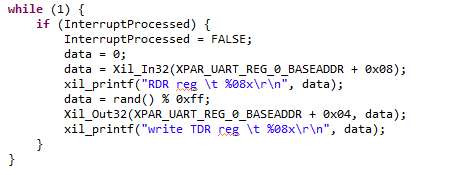

무한 루프 돌리는 부분에서는 Loopback Test를 한다.

인터럽트가 걸렸을 때 처리하는 코드는 아래와 같다.

전체 코드는 아래와 같다.

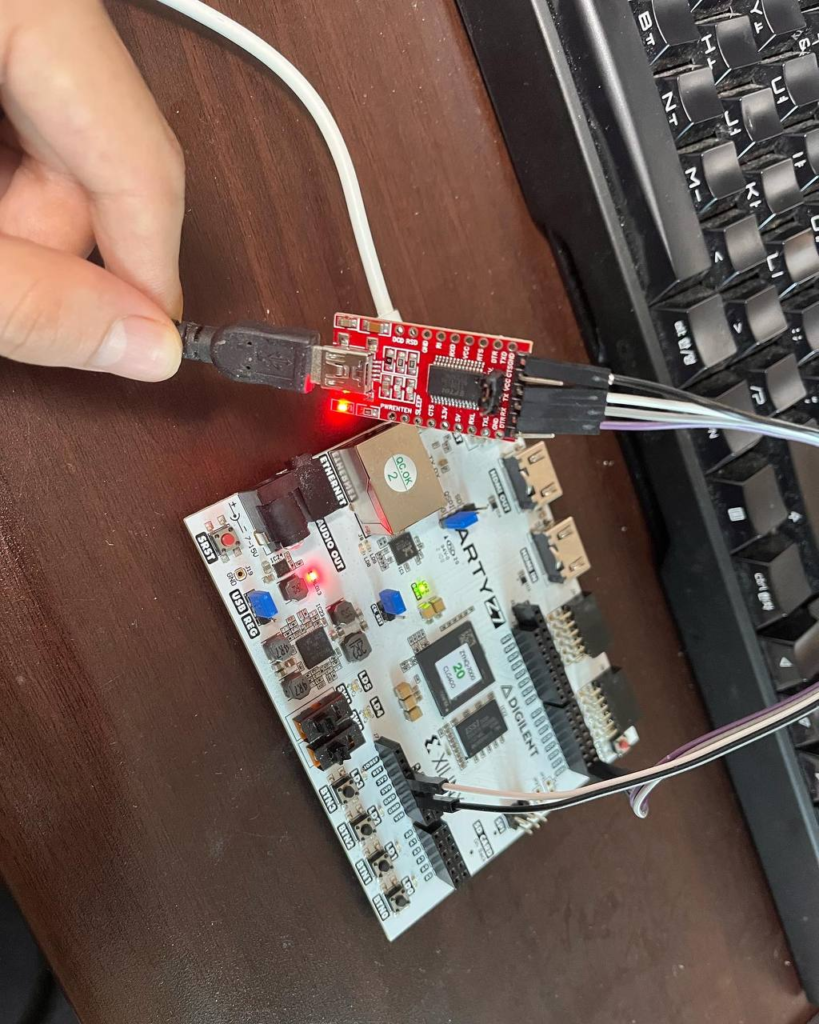

loopback 테스트가 아니고 아래와 같이 PC랑 물려서 테스트하려면 RTL 코드를 수정해야한다.

https://github.com/dk-min/verilog_study/tree/master/12.APB_UART/12.APB_UART.srcs

여기서 작업해야하는 것은 xdc 코드를 수정해야하고, uart_reg.v 파일도 수정해야한다.

포스팅 끗.