APB Bus 살펴보기 프로젝트

목차

- UART verilog Testbench 살펴보기

- UART Tx Verilog Module 살펴보기

- UART Rx Verilog Module 살펴보기

- APB Bus 살펴보기 (현재 포스팅)

- APB Register 설계하기

- Vivado UART 모듈 설정 하기

- Xilinx Zynq Firmware Code 짜보기

지금 만든 모듈 제어를 지금은 Testbench로 했지만, 실제로는 CPU로 제어해보고 싶을 수도 있다. 개인 취미로 CPU를 설계할 생각은 전혀 없기 때문에, 최종 목적은 FPGA로 물려서 테스트 해보려고 한다.

CPU에서 설계한 IP와 데이터를 주고 받는 방법은 여러가지가 있는데, 이번 예제에서는 가장 간단한 버스를 사용해보려고한다. APB Bus이다.

스펙에 대한 문서를 첨부하니 관심 있는 사람은 참고 바란다.

APB Bus는 무엇인가

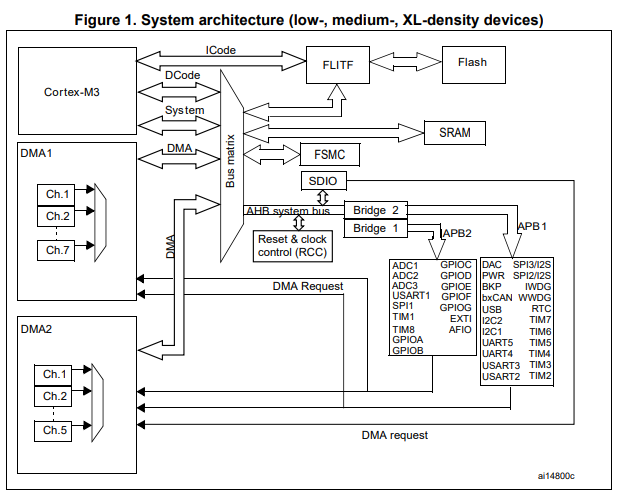

위에 보는 그림은 stm32f103 시스템 아키텍쳐이다. Cortex M3 코어에서 AHB Bus를 거쳐 AHB to APB 브릿지를 지난다음에 각 Peripheral을 제어하는 식으로 되어있다.

그러니까 CPU나 MCU에서 UART를 결국에는 APB Bus로 제어하는 것이라고 볼 수도 있다.

그러니까 그 전에 버스는 어떻게 되었는지 신경끄고 그냥 APB Bus에 지금 구현된 UART 모듈을 붙이면 되겠다.

UART 모듈에 붙이는건 머리가 아픈 일이니 나중에 생각해보고 먼저 APB 버스에 대해 알아보도록 하자.

APB Bus 들여다보기

간단하게 MCU에서 IP로 쓰는 경우를 가정해보자.

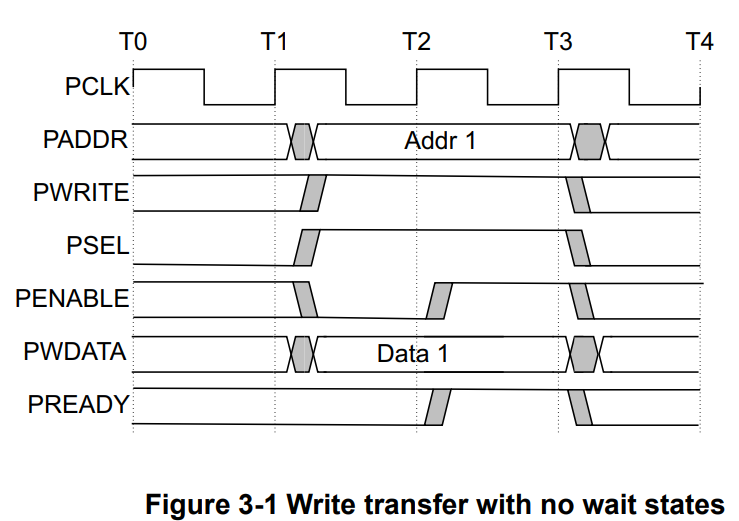

여기서 MCU에서 나가는 신호는 PCLK(클럭), PADDR(쓰고싶은 데이터의 주소), PWRITE(쓸건지 읽을건지), PSEL(Select Signal), PENABLE(Enable), PWDATA(쓸 데이터)이고 MCU가 읽을 신호는 PREADY(slv가 값을 저장한 준비가 되었음)이다.

데이터를 쓰고 싶으면 어떤 한 시점에 PADDR과 PWRITE와 PWDATA가 Valid할 때 PSEL을 High로 놓으면 된다. 그럼 그 다음 cycle에 PENABLE을 high로 놓고 PREADY가 high인 경우 다음 cycle에 PSEL과 PENABLE을 Low로 놓으면 된다. 세 줄 요약 간다.

- PADDR(addr), PWRITH(high), PWDATA(DATA), PSEL(high)로 설정

- 그 다음 cycle PENABLE(high)로 설정

- PREADY가 high인 경우 -> 그 다음 cycle에 PSEL && PENABLE goes low

여기서는 Write하는 경우이므로 PWRITE는 High여야 한다. 반대로 읽는 경우는 PWRITE가 Low여야 한다.

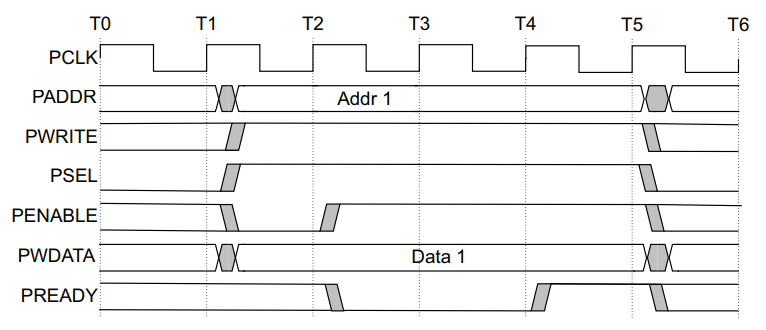

참고로 PREADY가 Low 상태로 지속되는 경우는 wait state로 유지되는데 아래와 같다.

기본적인 내용은 같고 PREADY가 low일 때는 현 상태가 계속 유지가 된다는 것이 포인트다.

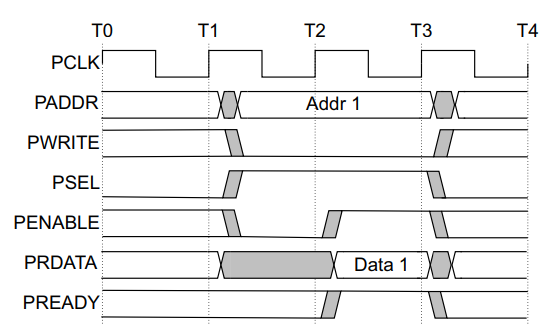

read 상태도 비슷하다 차이점이라곤 PWRITE가 low로 시작한다는 점 정도다. 그래서 자세히 설명 안하고 그래프만 첨부한다.

이 그래프를 첨부하는 이유는 나중에 APB Task Code를 작성해서 만든 APB Logic을 검증할 것이기 때문이다.