Vivado UART 모듈 설정하기

목차

- UART verilog Testbench 살펴보기

- UART Tx Verilog Module 살펴보기

- UART Rx Verilog Module 살펴보기

- APB Bus 살펴보기

- APB Register 설계하기

- Vivado UART 모듈 설정 하기(현재 포스팅)

- Xilinx Zynq Firmware Code 짜보기

이전까지 설계한 UART 모듈을 FPGA로 구현해서 돌려보는 것을 해볼 것이다. 코드는 깃 허브에 업로드 되어있다. 설계한 것들이 실제로 FPGA 상에서 돌아가는 것을 보면 신기하지 않겠는가

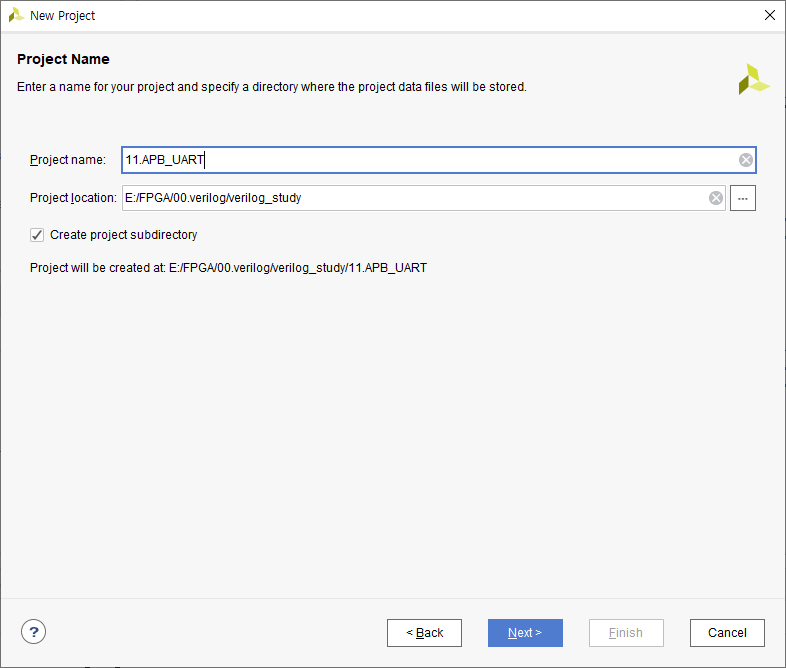

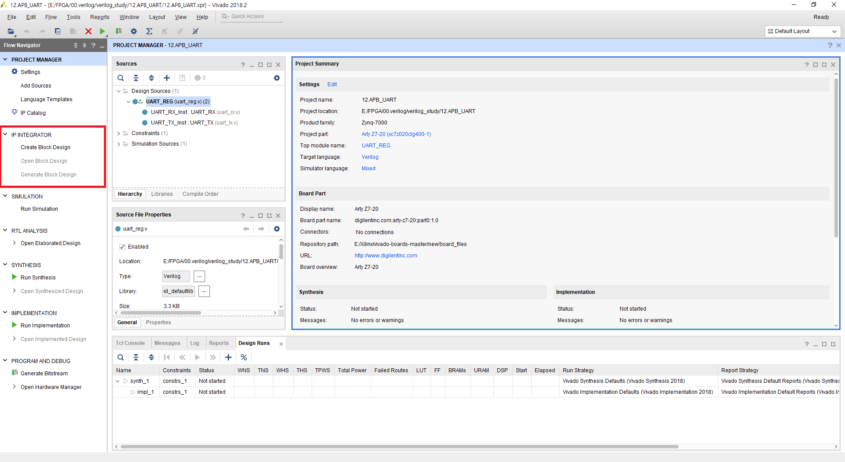

Vivado UART 프로젝트 설정하기

프로젝트를 하나 만들어준다.

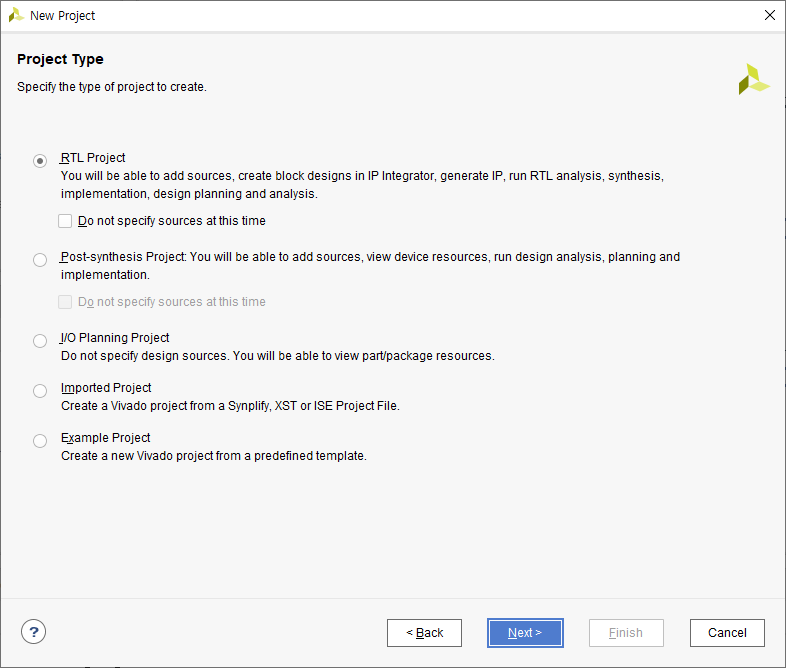

설계한 RTL을 물려서 할거니까 그대로 next 클릭

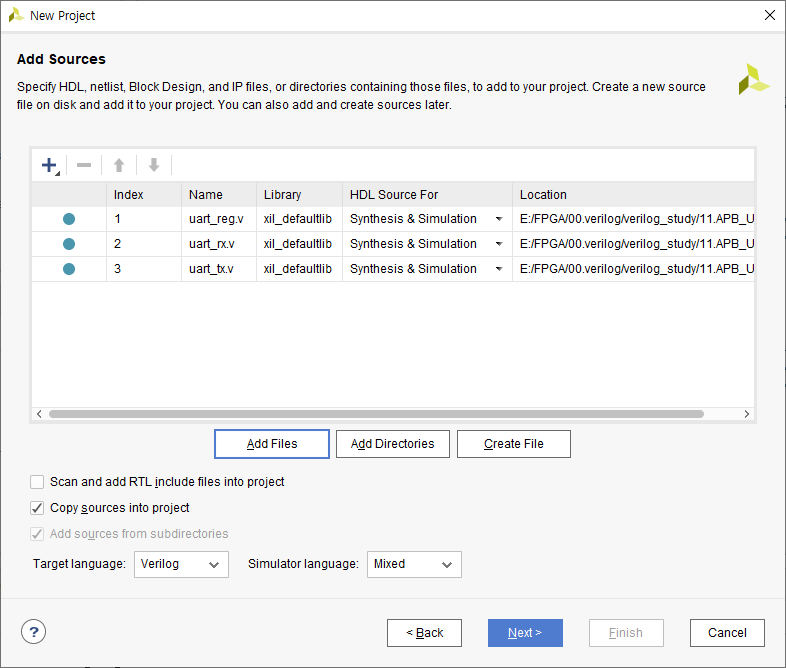

Testbench말고 RTL 소스 파일들을 추가해준다.

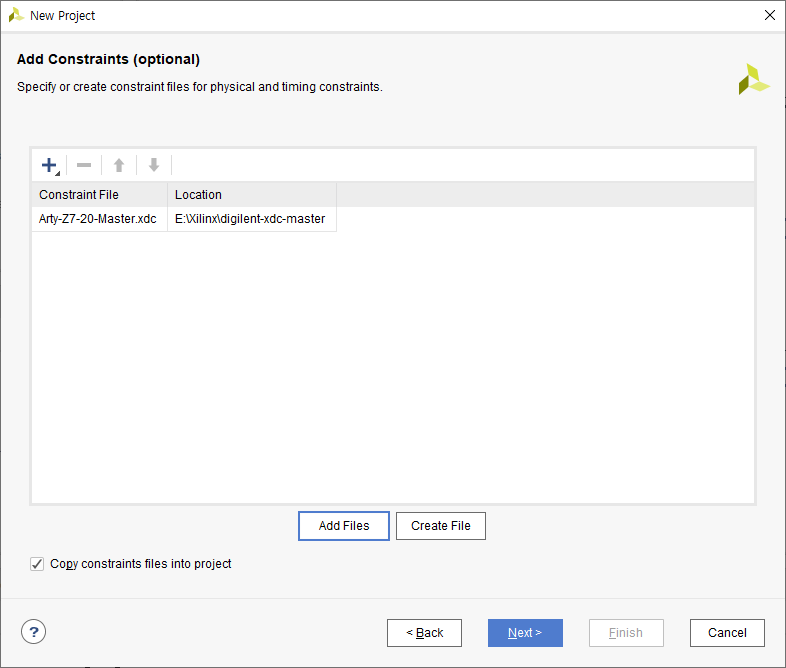

사용하는 보드의 xdc 파일을 추가해준다. 디질런트(Digilent) 보드를 사용하는 사람은 여기서 다운 받을 수가 있다.

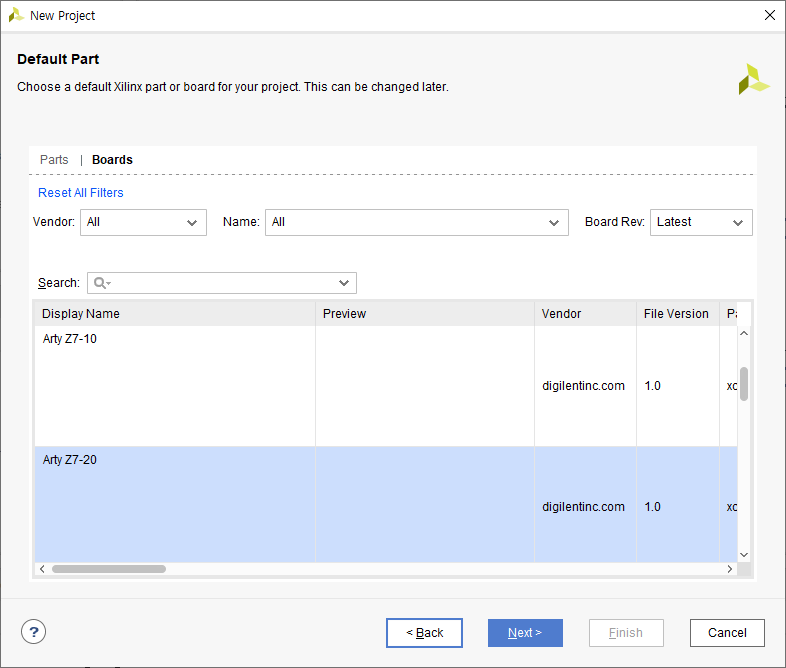

보드 설정을 블러온다. 디질런트 보드 사용 유저는 해당 링크를 참고해서 설정을 먼저 해주어야한다.

Vivado UART Block Design 진행하기

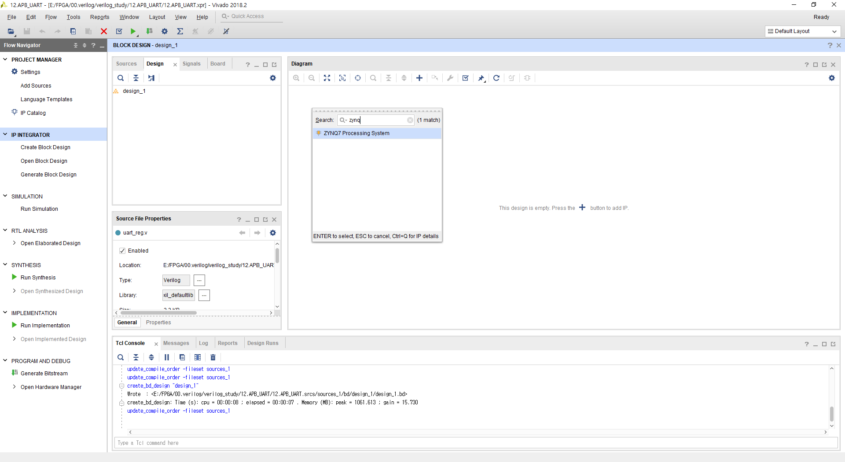

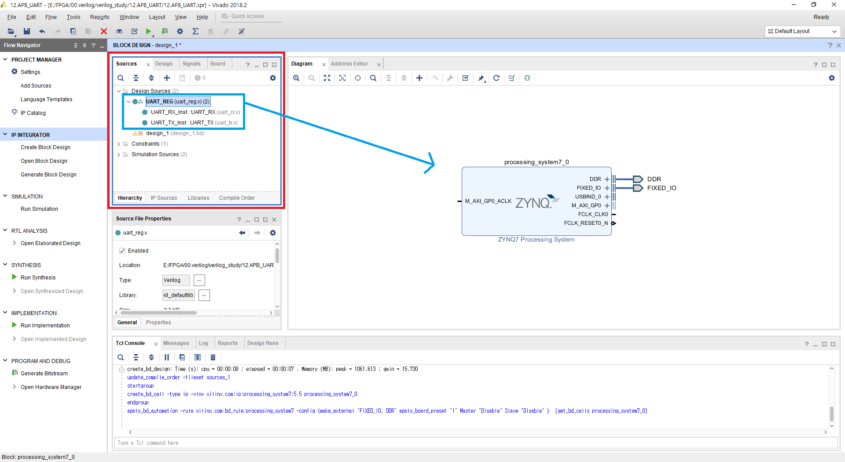

프로젝트가 생성되었으면 좌측의 IP INTEGRATOR에서 Create Block Design을 클릭하고 블록 디자인을 하나 만들어준다.

+버튼을 누르고 zynq를 눌러 하나 PS Core를 생성한다.(A9 ARM Core)를 생성

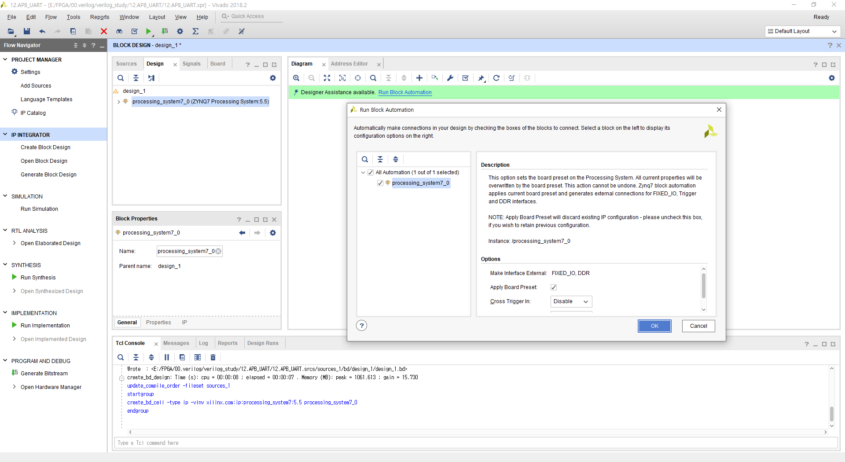

Run Block Automation을 눌러서 설정을 진행해준다.

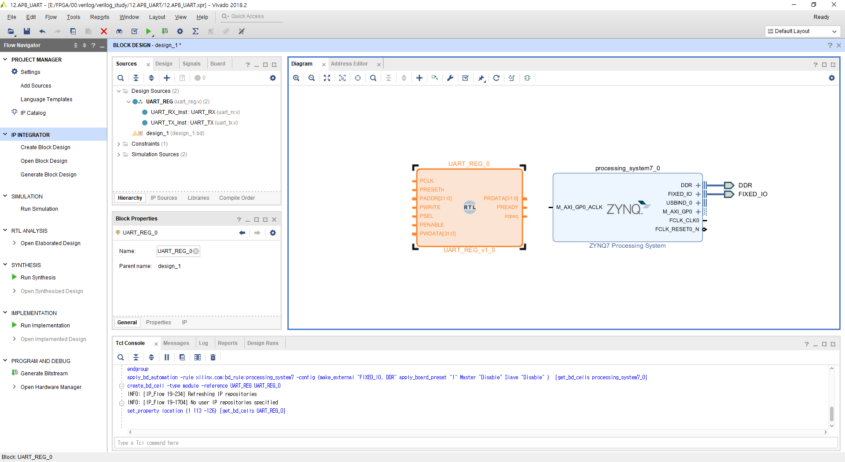

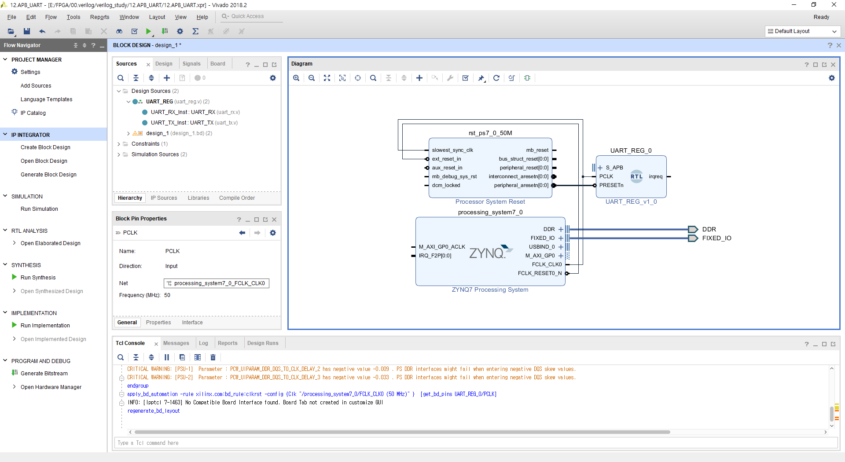

Source 탭으로 이동한 다음 설계한 모듈을 끌어다 놓는다.

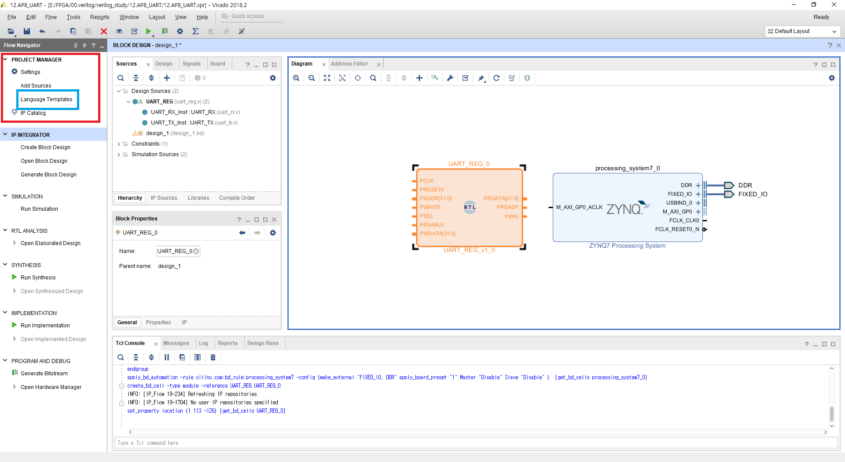

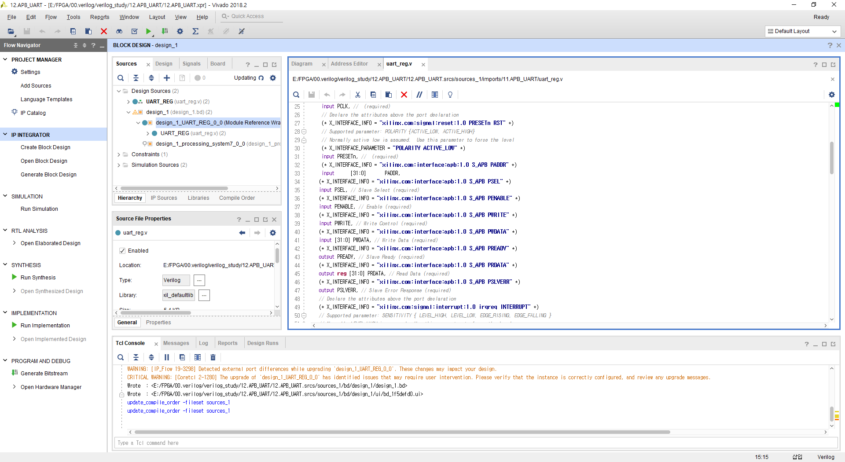

RTL 모듈이 추가되었다. Vivado 상에서는 설계한 모듈의 어느 포트가 APB 버스이고, 인터럽트이고, 클럭인지를 알 수가 없다. 이걸 지정해주는 코드가 있는데, 좌측의 Language Templates를 이용해야한다.

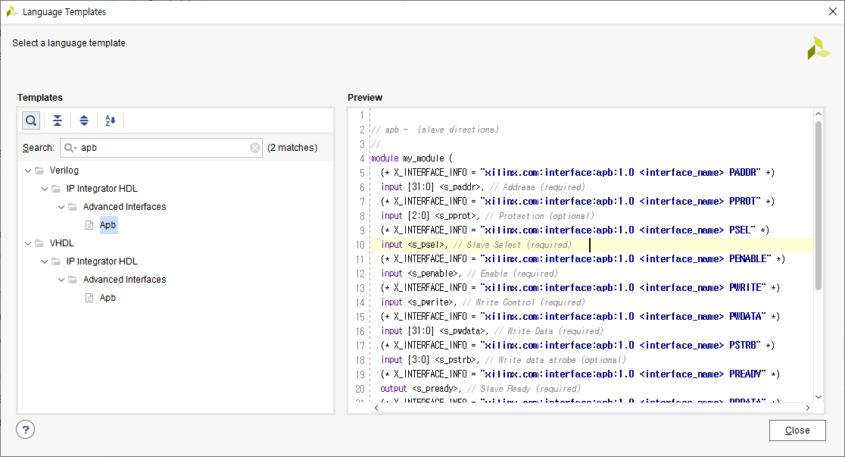

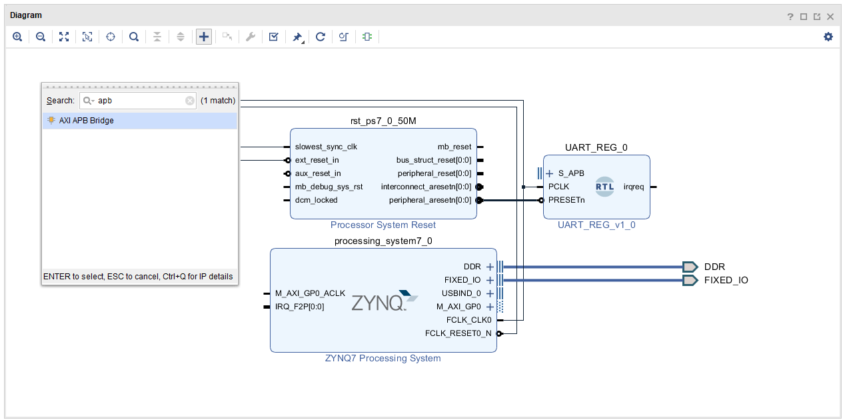

apb를 검색하고 해당 템플릿을 긁어야한다.

이런식으로 템플릿을 사용해서 각 포트 별로 지정해서 사용하면 된다.

인스턴스 연결한 것도 다르고, 합성 가능하게 코드를 좀 수정하였으니 깃허브 코드를 참고해야한다.

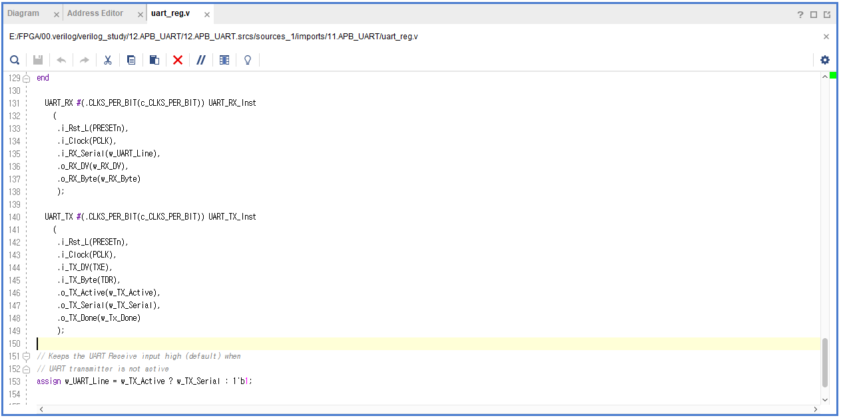

저장하고 다시 돌아가면 블록이 바뀌어져 있는 것을 볼 수있다.

CPU와 RTL 연결해보기

그리고 Run Connection Automation이 생성 되는 것을 볼 수 있다. (삽질 과정이 좀 많았는데, 바로 해결할 수 있는 방법으로 안내한다.)

무턱대로 누르지 말고 설정을 하나하나 해보자. 설정해야 할 것은 크게 3가지로 나눌 수 있다.

- APB Bus를 CPU랑 연결하기

- 클럭(50Mhz)과 Reset(Low active)설정해주기

- Interrupt 설정해주기

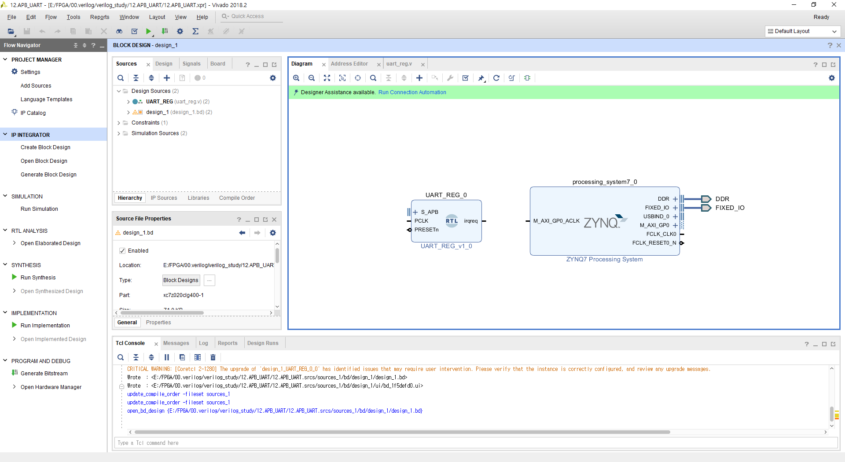

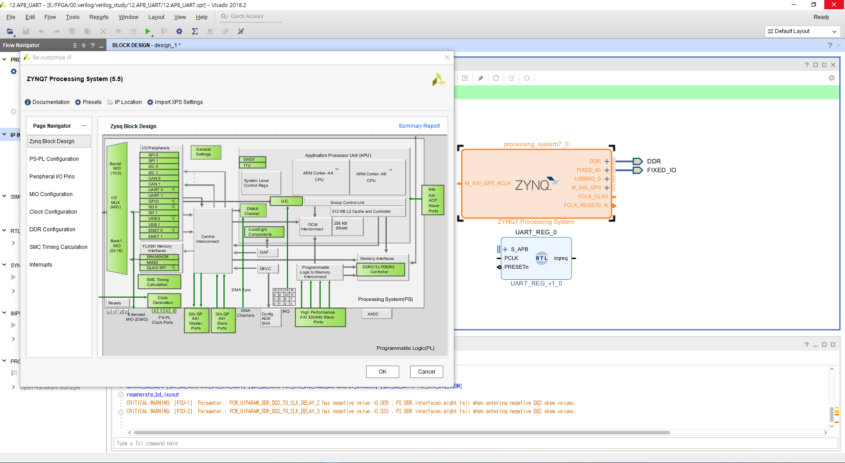

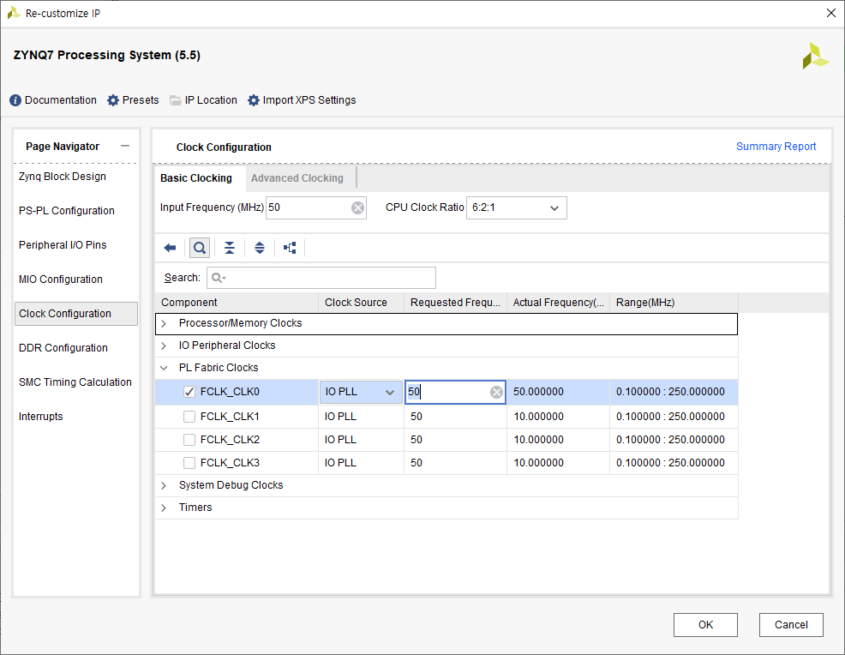

일단 클럭부터 설정해보자. zynq7를 더블클릭한다.

Clock Configuration 탭으로 가서 PL Fabric Clocks 탭에 CLK0를 50Mhz로 설정한다.

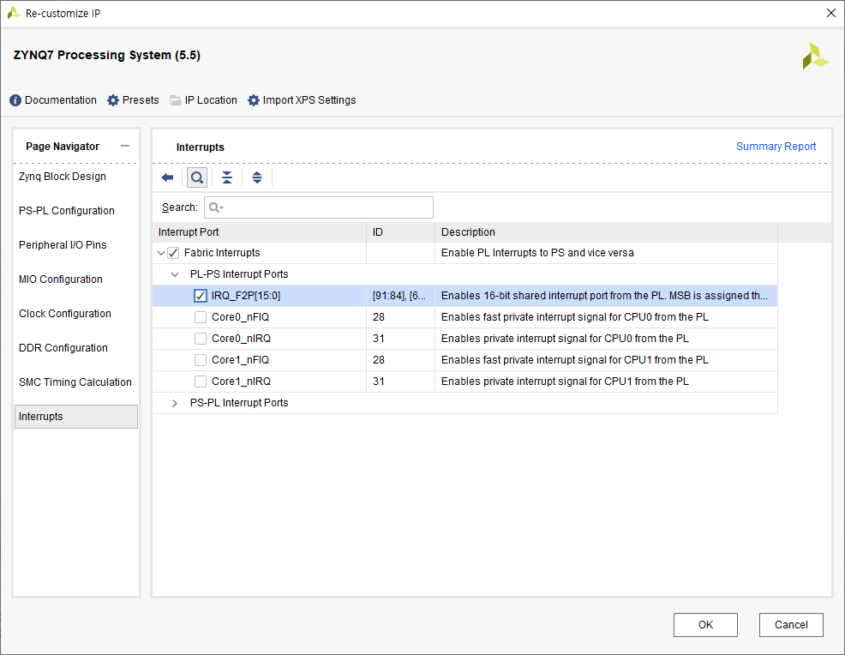

Interrupts 탭으로 가서 Fabric Interrupts PL-PS 포트 중에서 IRQ_F2P를 활성화 해준다.

이제 Runconnection Automation을 클릭해서 클럭 설정을 해준다.

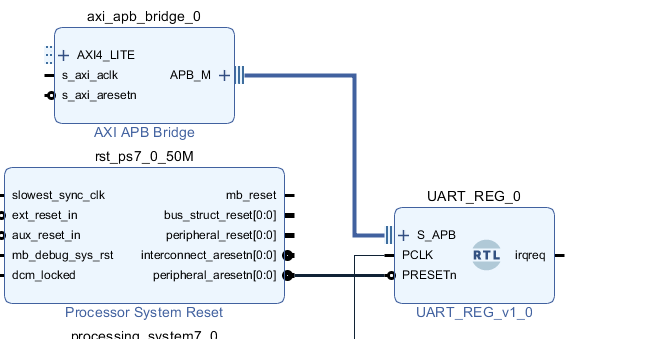

이쁘게 설정해주는 것을 볼 수 있다. 이제 APB 버스 설정을 해준다.

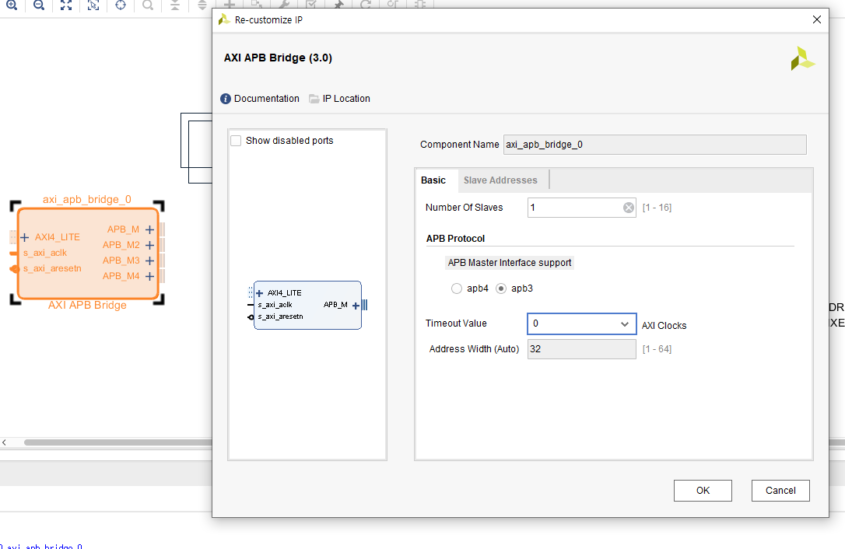

상단의 +버튼을 누르고 AXI APB Bridge를 누른다. 그럼 하나가 생성되는데 브릿지를 더블클릭해줘서 설정을 좀 해줘야한다.

슬레이브 갯수를 1개로 수정해주고 Ok한다. APB_M과 S_APB를 서로 연결해준다.

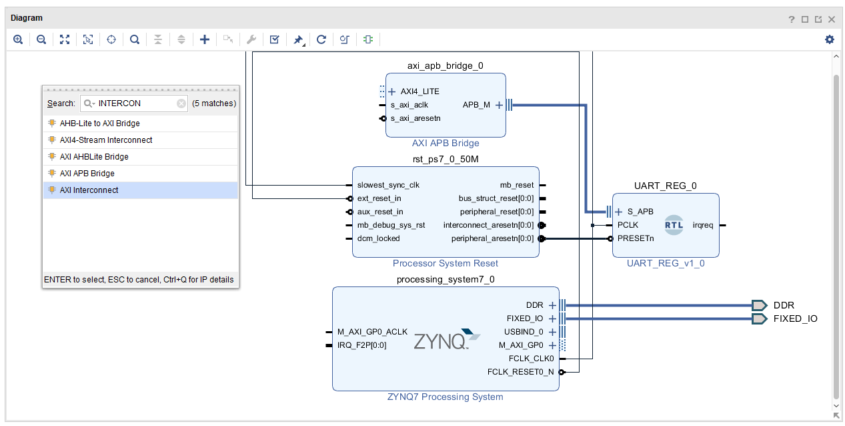

쨘. 이제 AXI4_LITE를 해결해야한다. INTERCONNECT를 검색해본다.

이놈을 추가해준다.

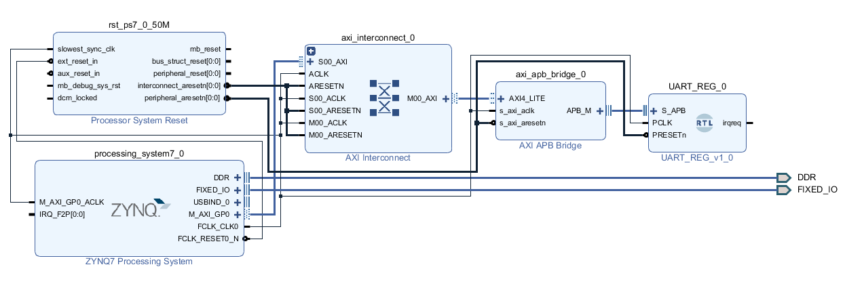

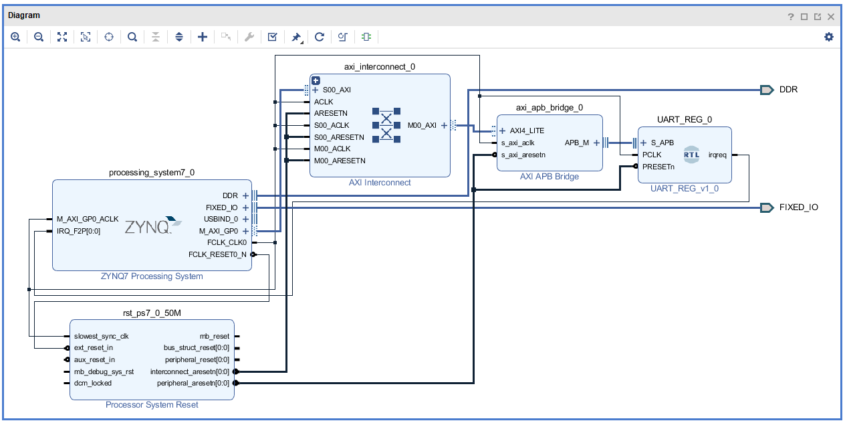

Interconnect도 갯수를 1개로 설정해주고 클럭과 리셋, AXI 연결을해준다.

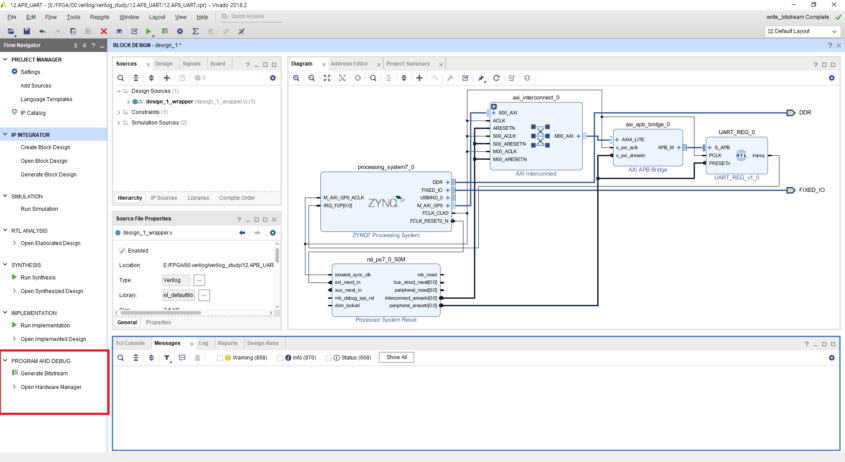

ZYNQ7 프로세서 GP0는 인터커텍터 S00_AXI로 가고 M00_AXI는 AXI4_LITE로 연결해준다. 클럭과 리셋도 다 연결해준다음 마무리로 irqreq를 IRQ_F2P로 연결해주면 모든 연결은 다 된다.

다 연결되었으니 F6을 눌러서 오류를 확인해본다. 그럼 기가막히게 오류가 난다.

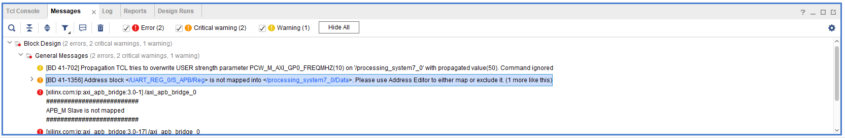

하단의 문제를 보면 어드레스가 연결안되었다고 누르는데 파란 글씨를 누르면 Address Editor가 뜬다.

레지스터 우클릭 – Assign Address를 해주면 된다.

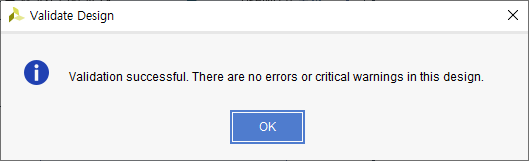

그리고 다시 F6을 누르면 문제가 없다고 나온다.

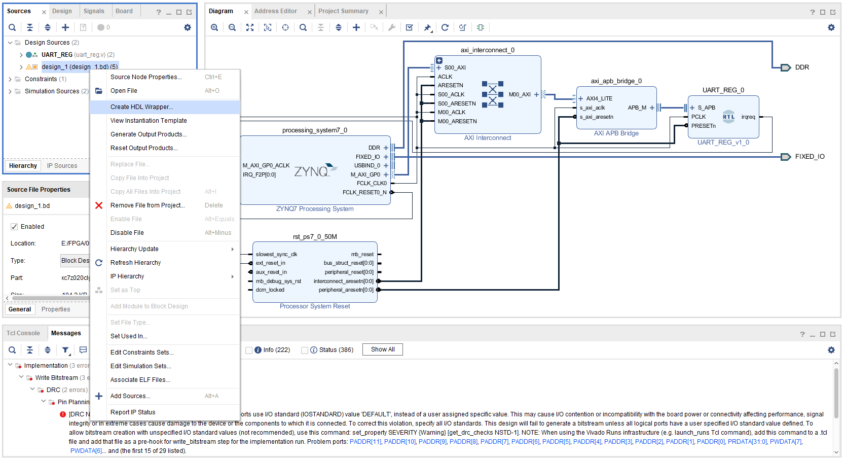

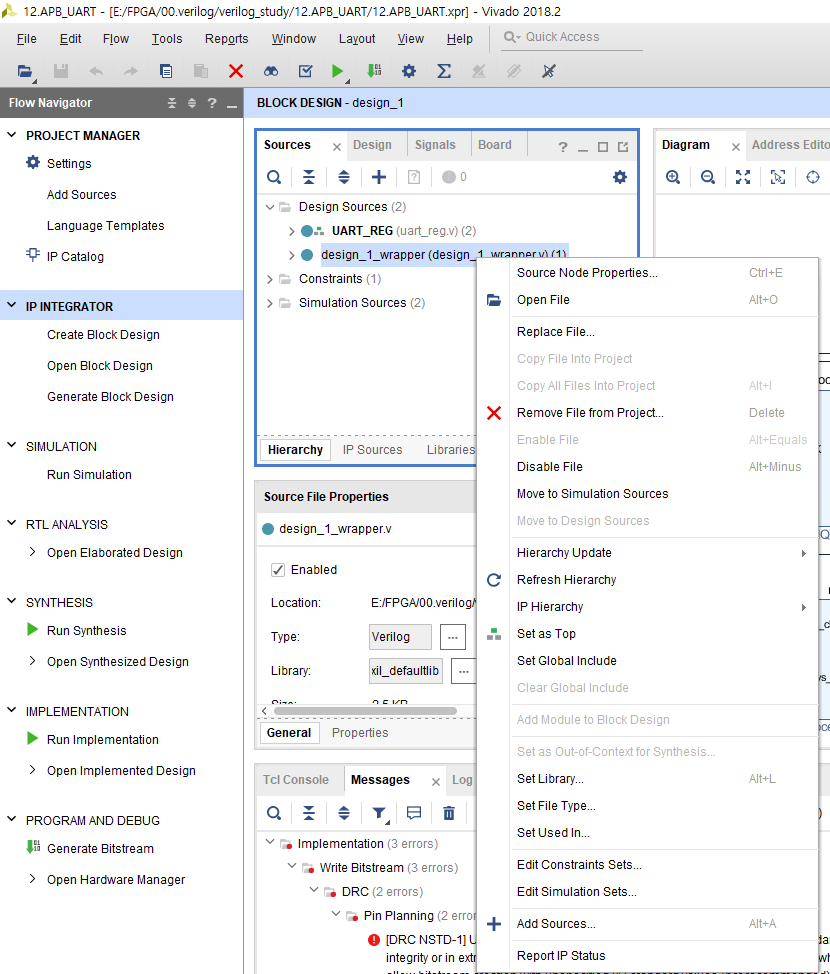

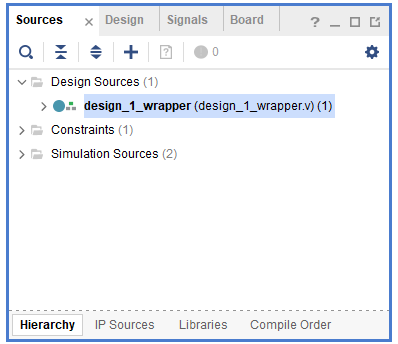

UART_REG가 TOP 디자인으로 되어있는데, 옳지 못하다. 실제로 비트스트림 생성을 하면 에러가 발생하는 것을 볼 수 있다. design_1 우클릭 – HDL wrapper를 씌운다.

Set as Top을 지정해준다.

편 – 안

이제 비트 스트림을 뽑아본다.

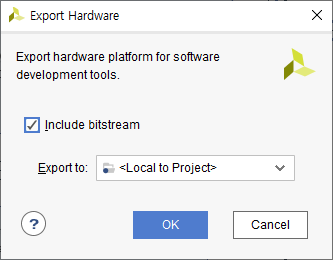

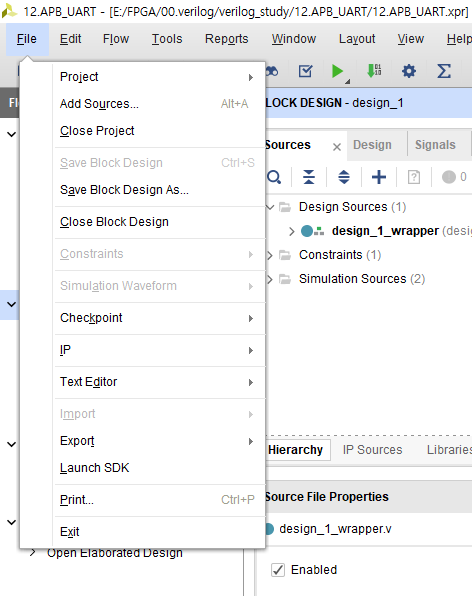

다 뽑았으면 하드웨어를 export를 하고 Include bitstream을 체크한다음 ok한다.

그 다음 Launch SDK를 실행해서 코드를 작성하면 된다.

끗

선생님..fpga정신 나갈것같아요..살려주세요

저도 잘 몰라요 선생님..