APB Register 설계하기

목차

- UART verilog Testbench 살펴보기

- UART Tx Verilog Module 살펴보기

- UART Rx Verilog Module 살펴보기

- APB Bus 살펴보기

- APB Register 설계하기(현재 포스팅)

- Vivado UART 모듈 설정 하기

- Xilinx Zynq Firmware Code 짜보기

이전 포스팅에서 살펴본 APB Bus로 접근할 수 있는 APB Register를 설계할 것이다. UART의 상태를 확인할 수도 있고, 설정을 해줄 수도 있고, 데이터를 쓰거나 저장할 수 있는 레지스터를 만들어 볼 것이다. 이번에 다룰 코드는 깃허브에 업로드 되어있다.

UART 레지스터

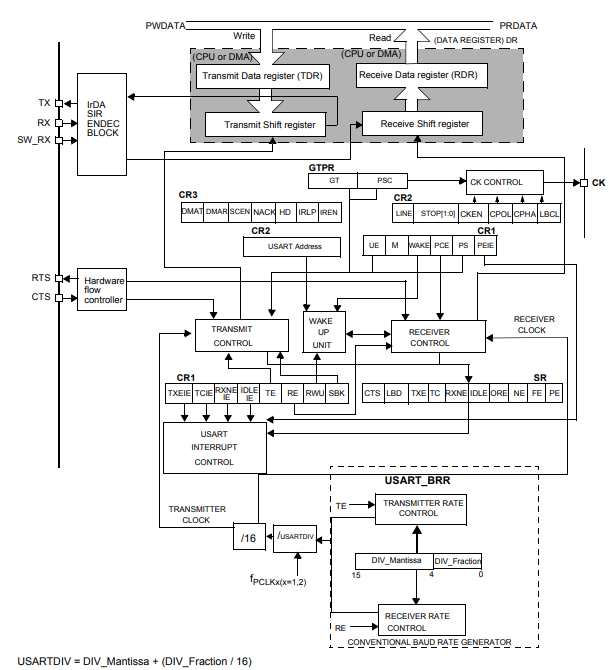

기존에 설계한 UART 모듈에 APB로 통신하는 레지스터를 만들어 붙일거다. 흔히 많이 보던 stm의 데이터시트를 먼저 보고 설계를 진행해보자.

APB Register 구조 파악해보기

위 그림을 보면 APB Register구성을 확인해볼 수 있다. TDR, RDR을 apb bus로 제어해서 값을 읽고 쓰는게 가능하고, 상태 레지스터도 있고, baud rate를 설정할 수 있는 레지스터도 있다. 여기에 나온 것들을 다 구현하지는 않을거고, 일부만 구현해보기로 한다.

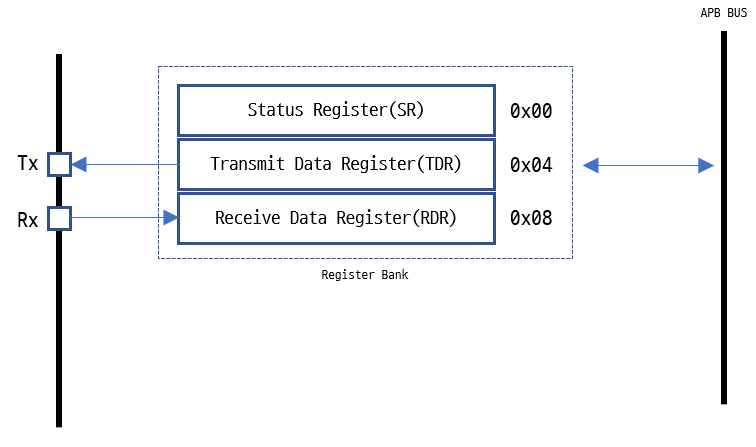

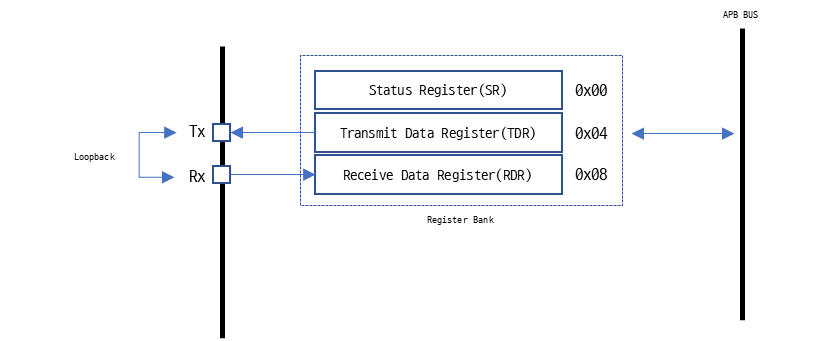

APB Register 구조 잡아보기

0x00 번지의 레지스터는 상태와 설정을 할 수 있는 레지스터를 설정

0x04 번지의 레지스터는 tx로 전송할 데이터를 저장하는 레지스터로 설정

0x08 번지의 레지스터는 rx로 송신된 데이터를 저장하는 레지스터로 설정한다.

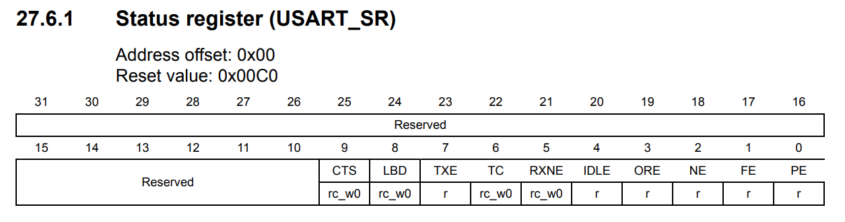

보통의 데이터시트에서는 아래와 같이 각 레지스터의 값들을 명기하게 되어있다.

그치만 나는 복잡하게 만들 생각이 전혀 없어서 0번 5번 7번 비트만 사용해서 구현을 했다. 기능은 위에 적힌 레지스터랑은 좀 다르다.

- 0번 비트 – enable 비트. 1로 설정하지 않으면 모듈이 동작안함

- 5번 비트 – rx 데이터가 들어오면 1로 설정. 레지스터가 비어있으면 0으로 설정된다.

- 7번 비트 – TDR에 데이터를 쓰면 1로 설정. 송신이 완료되면 0으로 설정된다.

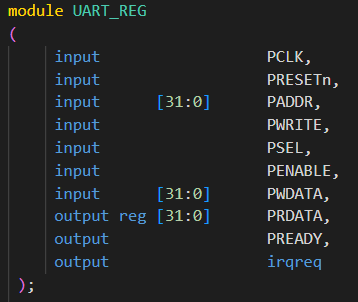

이번에 설계한 모듈은 Slave 모듈이므로 이를 고려해서 설계를 진행하면 된다.

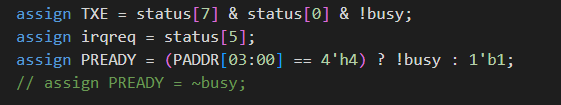

모듈에서는 APB Bus와 인터럽트 신호를 하나 만들었다.

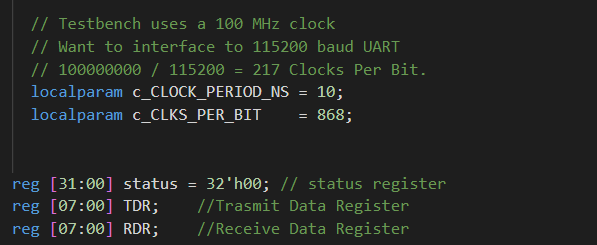

레지스터를 세 개 만들어준다.

대충 PREADY 조건, 인터럽트 조건 등등 여러 조건등을 정의해준다.

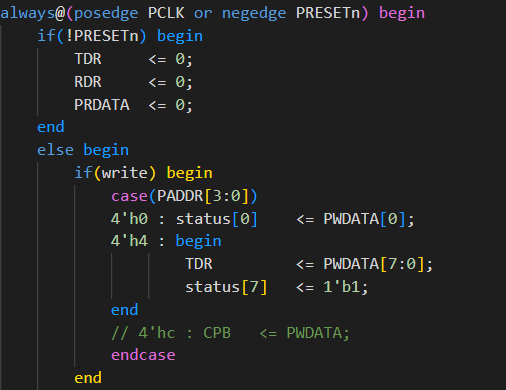

리셋 될 경우 초기화해주고 쓰기 상태일 때 주소에 따라 기능을 정의해준다.

상태 레지스터의 경우 0번 비트를 제외하고는 쓰기가 불가능하게 해두었다.

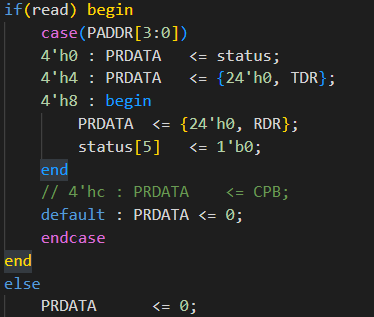

읽기 상태일 경우 각 주소에 따라 값을 읽을 수 있도록 정의해두었다.

0번 주소일때는 상태 레지스터를 읽고

4번 주소일때는 TDR 값을 읽고

8번 주소일 때는 RDR 값을 읽고, 레지스터가 비워졌음을 저장한다.

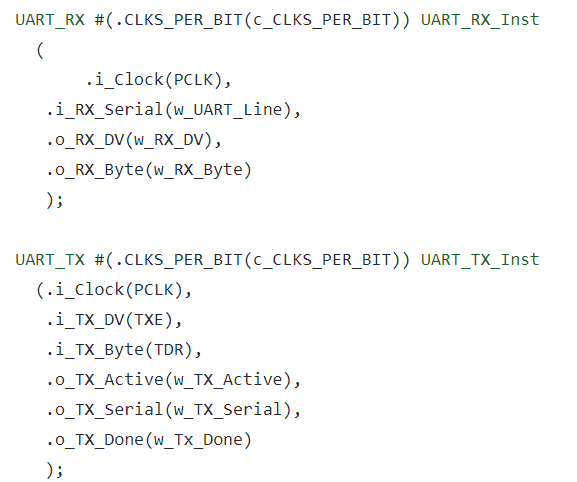

여하튼 원하는 기능을 다 구현한다음에 기존에 구현해놓은 UART 인스턴스랑 연결해준다.

보면 알겠지만, loopback으로 설정해서 검증을 진행했다.

Tx에다가 값을 쓰면 알아서 Rx통해서 RDR에 저장되는 식이다. 그래서 보낸거랑 같은지 검증하면 되는 식으로 진행할 것이다.

테스트 벤치는 요 링크 참고하면 된다.

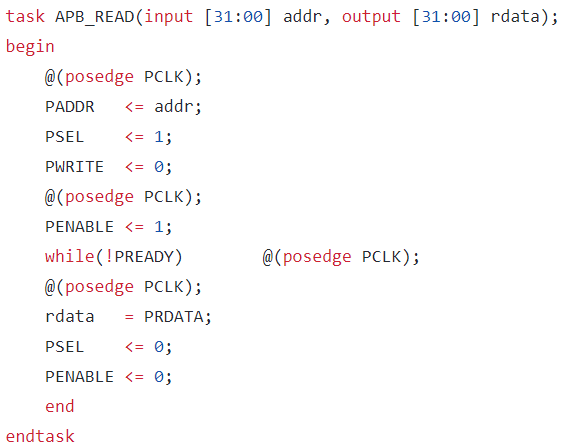

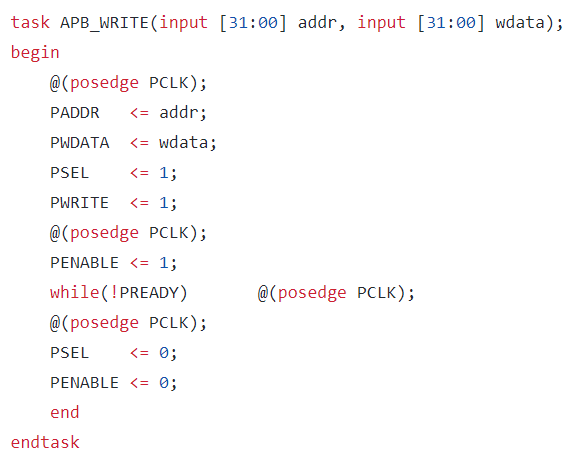

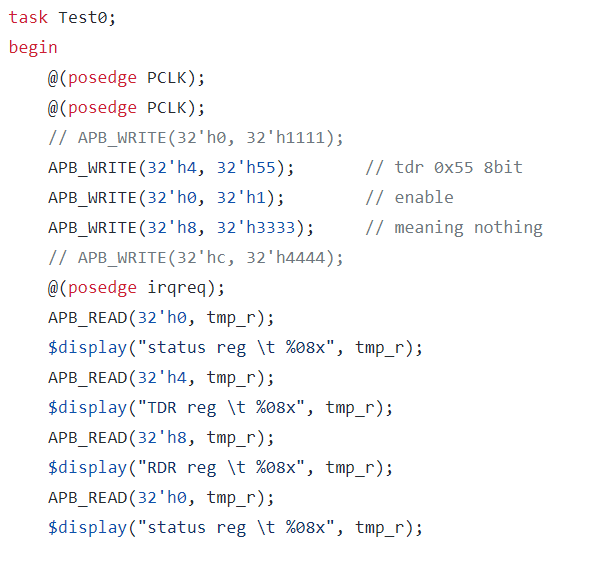

이런식으로 스펙에 정의된 대로 APB 테스크를 만들어주고

내가 원하는대로 테스트 벤치를 만들어서 놀면 된다.

여하튼 내가 원하는대로 잘 되는 것을 확인했다.

그럼 레지스터 포스팅 끗!