목차

- VITIS HLS 찍먹 해보기 – AXI 기초지식 편

- VITIS HLS 찍먹 해보기 – 기초 코드 이해해보기 (현재 포스팅)

- VITIS HLS 찍먹 해보기 – 기초 드라이버 작성해보기

INTRO

지난번 포스팅에서 AXI Lite의 기초에 대해 알아보았다.

이번에는 HLS 코드를 바탕으로 Waveform을 한번 찍먹해보자.

VITIS HLS에 대한 설명은 여기 가서 찍먹해보길 바란다.

Vitis HLS 코드 찍먹해보기

이번에 선택한 예제는 simple adder이다.

a + b = c다.

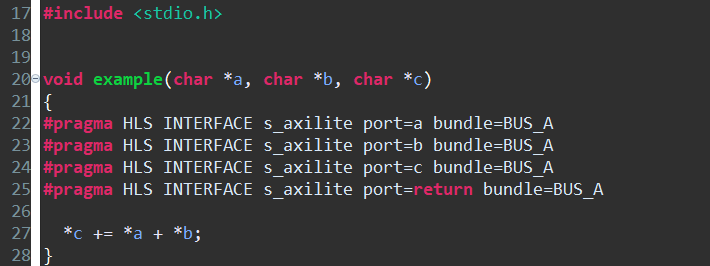

코드는 별거 없다. HLS에서는 #pragma를 많이 사용하는데, Pipeline이나 unroll과 같은 지령에따라 생성되는 하드웨어가 달라지므로 알아보는 것이 좋다.

해당 코드에서는 a, b, c와 interrrupt와 control register 등을 bundle로 묶어서 사용하고자 #pragma HLS INTERFACE s_axilite port로 묶어서 사용중이다.

s_axilite는 axi-lite slave를 의미한다.

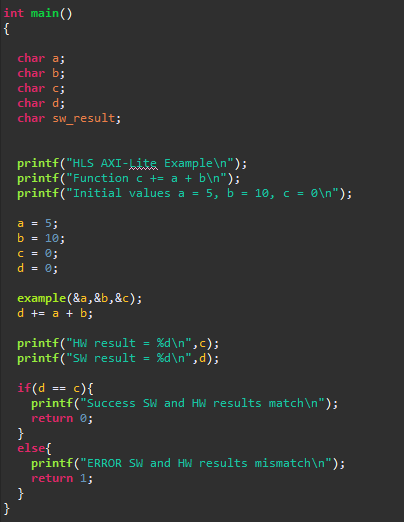

해당 IP를 검증하는 것도 C 코드로 검증하는데, 이또한 간단하다.

a,b는 입력이고 c는 HLS Block의 output, d는 software로 생성한 output이다. 똑같은 adder인데 결과가 다르다면 HLS Block에 문제가 있다고 봐야할 것이다.

다만 d = a + b;가 아니고 d += a + b인지는 잘 모르겠다. 어차피 결과는 같겠지만.

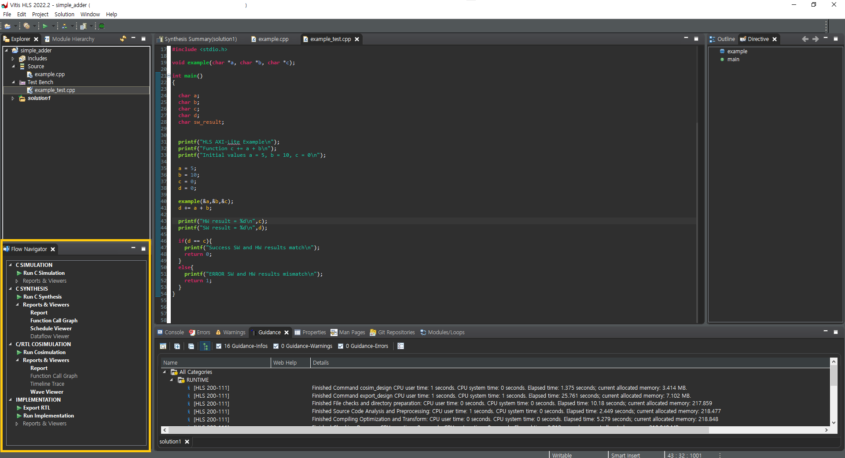

좌측 하단에 flow navigator로 Run C Simulation을 눌러보자.

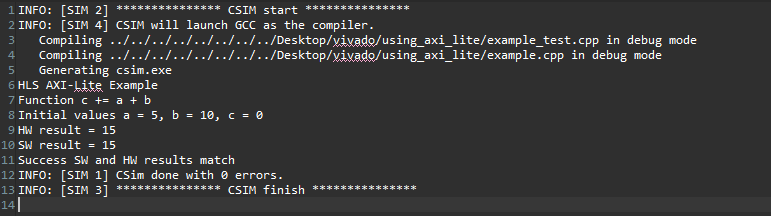

결과를 보면 설계는 성공적으로 진행된 듯 싶다.

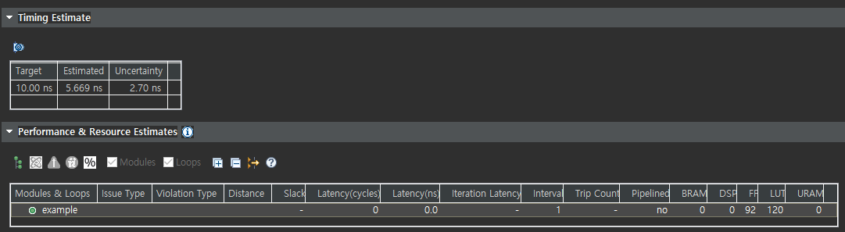

Run C Synthesis로 합성하고 결과를 보자.

타이밍도 널럴~하게 잡혔고 사용량도 별로 없다.

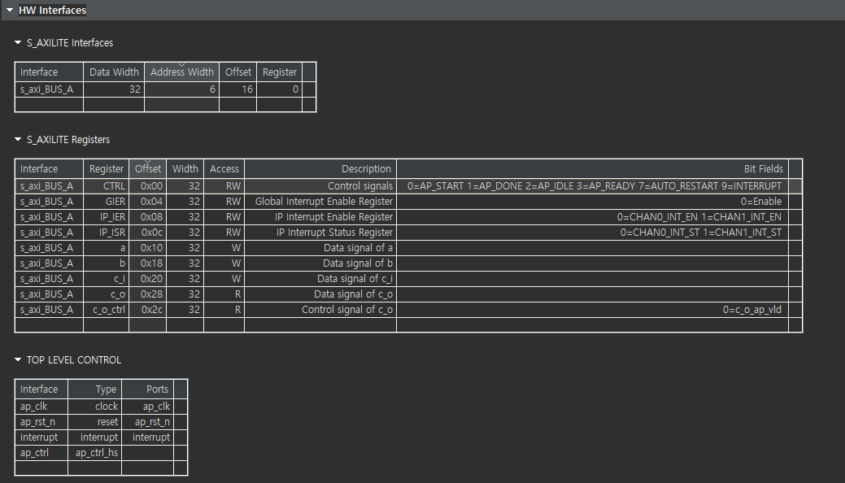

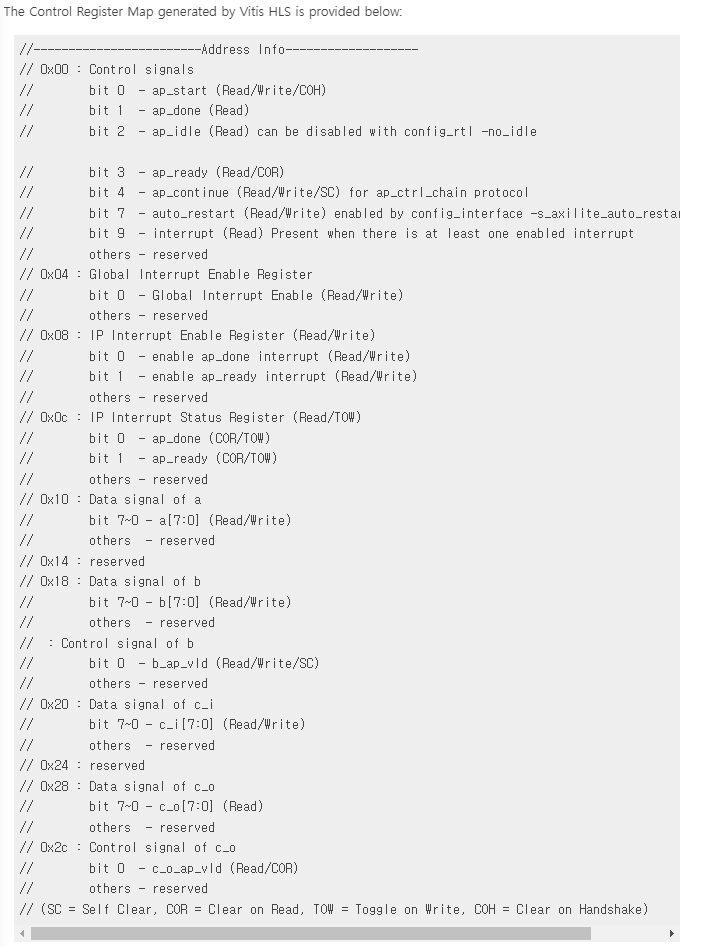

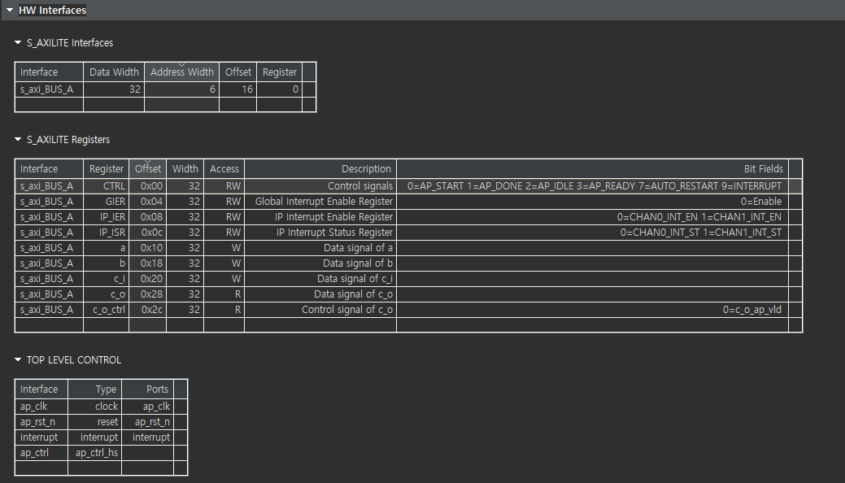

컨트롤 레지스터, 인터럽트 레지스터, data 레지스터 등이 생성되어 있는 것을 볼 수 있다.

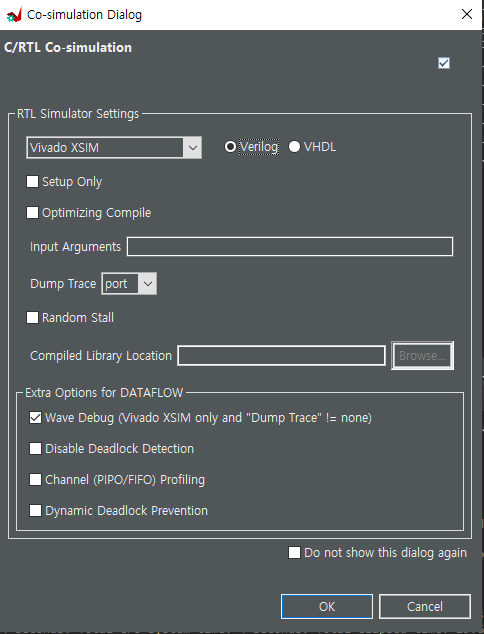

그럼 두근두근 cosim을 돌려서 waveform을 보자.

만약에 vivado말고 modelsim같은거 있으면 그걸로 돌려봐도 된다.

Waveform 찍먹해보기

두근두근 waveform과 함께하는 데이트 시간이다.

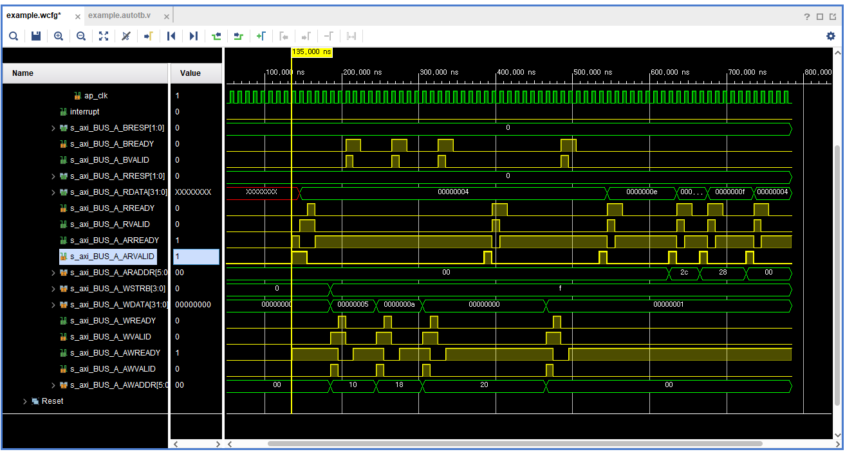

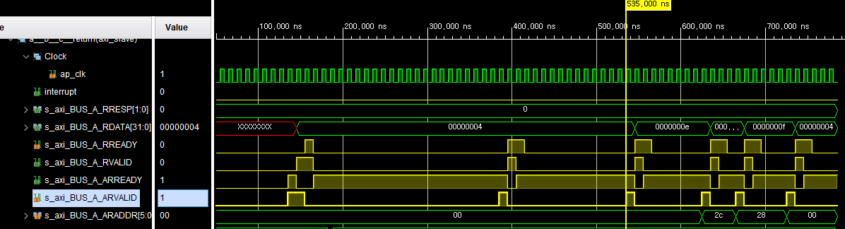

보통 read가 먼저일 때는 ar -> r 채널순으로 보면 대충맞고

write일 때는 aw -> w -> b 채널 순으로 보면 맞다. 반박시 님 말이 맞음.

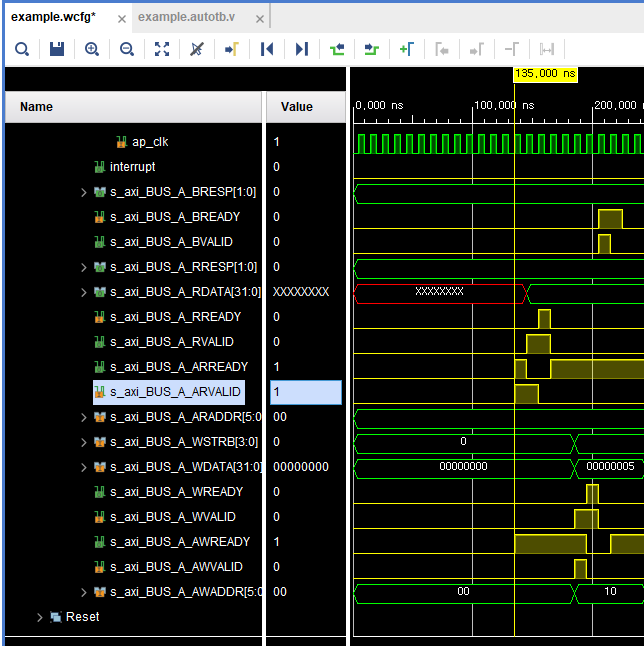

먼저 AR 채널에서 ready – valid handshake하는 지점을 본다.

대충 135ns 정도 되는 지점인데, 이때의 ARADDR이 0이다. 이 말은 대충 0번지 데이터 내놔라는 뜻이다.

그 다음에 R채널에서 ready – valid handshake하는 지점을 본다.

대충 155ns 되는 지점이고 이때의 rdata의 값이 4이다. 따라서 아래와 같이 정리 가능하다.

- master : 나 0번지 데이터 내놔

- slave : ㅇㅇ 4임

그럼 0번지는 뭐하는 놈이냐?

Control signal이라는 놈이고, 4는 0100이므로 ap_idle 상태라는 뜻이다.

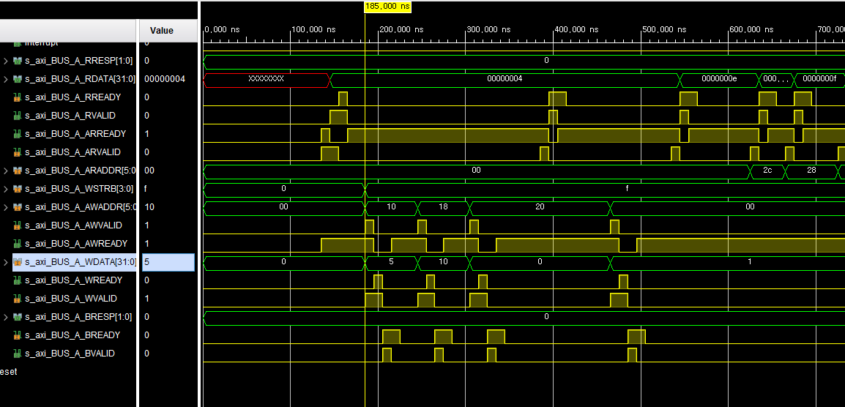

그럼 오케이. 그다음 동작을 보자. write operation인데, 방식은 같으므로 aw w b채널을 묶어서 설명한다.

185ns 부근에서 0x10에 5의 데이터를 쓰라고한다음 b채널로 response 받고, 그다음 0x18에 10을 쓰고, 0x20에 0을 쓰라고 한다음 0x00에 1을 쓴다.

무슨 의미인지 한번 보자.

보면 0x10은 a, 0x18은 b, 0x20은 c_i이다. 따라서 a는 5, b는 10, 결과를 담는 c는 0으로 초기화 한 것이다.

그리고 0x00에 1을 입력한 것은 ap_start 지령을 주었음을 알 수 있다.

a,b,c 입력 넣고 요이땅 했다는 뜻이다.

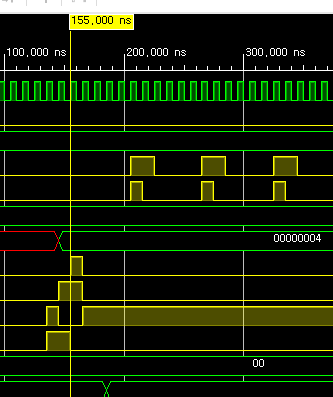

그 다음에는 0x00에 대한 read를 다시 요창하고 e(14)의 값을, 0x2c는 1의 값을, 0x28에서는 f의 값을, 마지막으로 0x00에서 4의 값을 회신받았다.

해석해보자.

- control signal(0x00)은 14가 발생함. 이는 1110을 의미하고, 상기 표에 따라 ap_ready, ap_idle, ap_done을 의미한다.

- control signal of c_o(0x2c)에서 output에 대한 data가 valid함을 알려줌

- c_o(0x28)에서 f(15)의 값을 읽었다. 이는 a = 5, b = 10이므로, c=15가 되어야 하는데, 하드웨어 역시 같은 값을 보내주고 있음을 알 수 있다.

- control siganl(0x00)에서 ap_idle 상태로 돌아갔음을 알려준다.

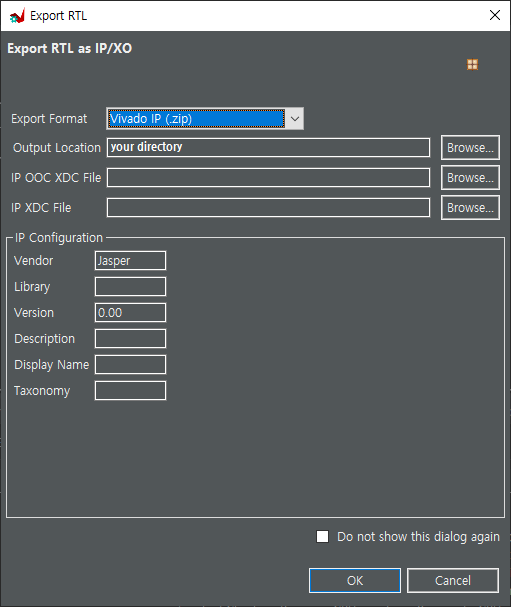

설계가 성공적으로 마무리 되었으면, Export RTL해서 저장하면된다.

자세한 내용은 문서를 확인해보거나 가지고 놀아보기를 바란다.

다음 포스팅에서는 vivado에서 실제로 ip를 연결해보고, cpu로 돌려보는 것으로 하겠다.