STM32F103 보드 설계

연구실에서 떠야하는 PCB가 생김에따라 먼저 간단설계먼저 포스팅한다.

아래에 언급할 설계도에서는 부가회로없이, ST-LINK만 동작시킬 수 있도록만 설계했다. 만약에 외부 크리스탈을 사용하거나, RTC를 사용할 경우 데이터시트를 읽어보세요. 요청이 있으면 첨부해 드리겠습니다.

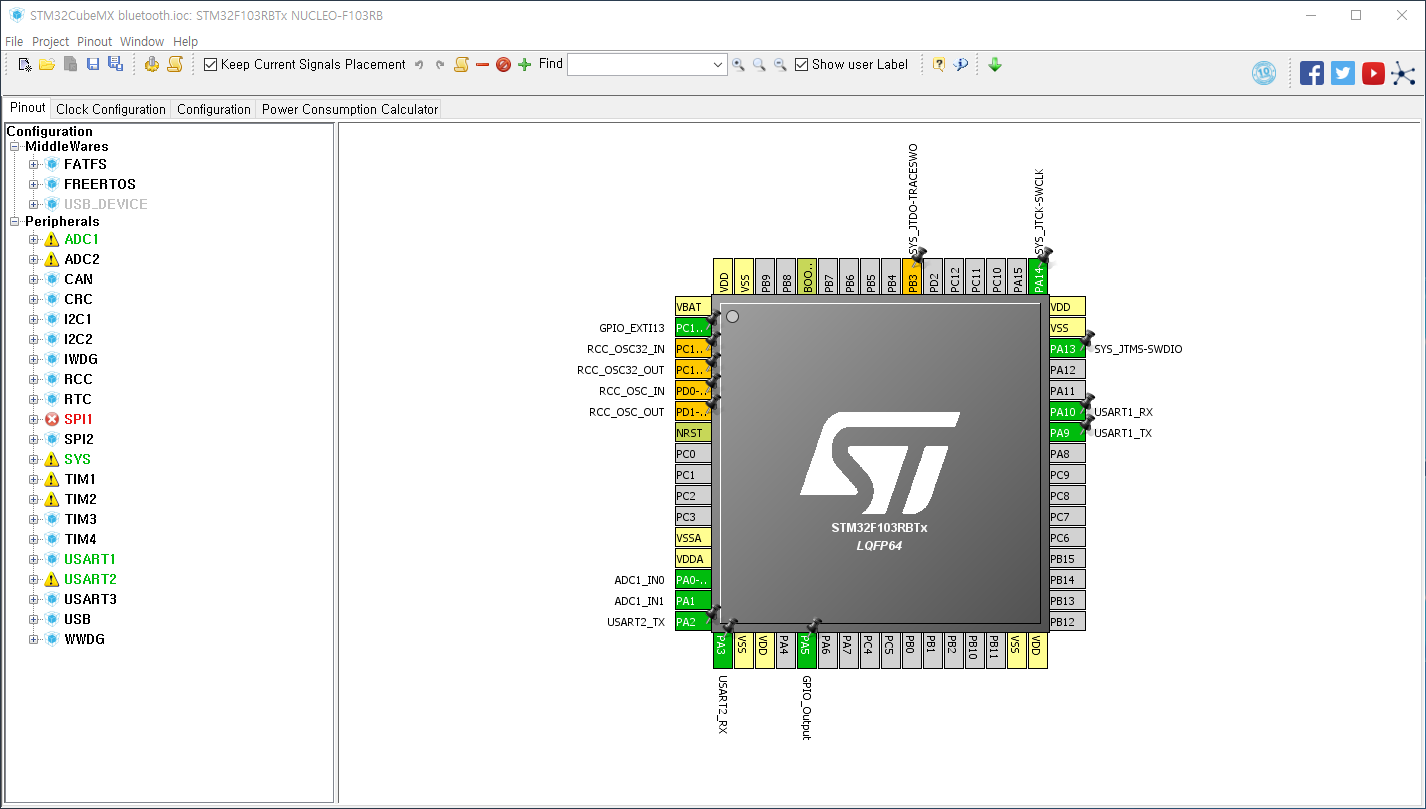

STM32F103을 설계하려면 데이터시트에서 PINMAP을 찾아아하지만, CUBEMX를 사용하면 수고로움이 덜어진다.

Nucleo64 중에서 F1시리즈를 사용하는 유일한 보드다. 칩은 F103RBT*를 사용한다. 위의 회로에서 기본적으로 사용할 회로는 디버깅이랑 리셋회로, BOOT0설정 뿐일 것이다.

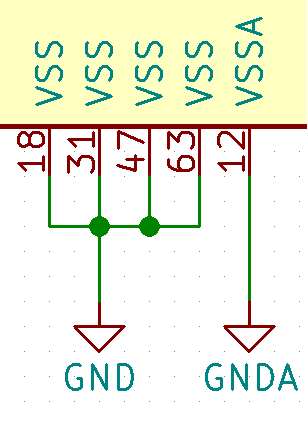

먼저 전원 핀을 모두 연결해야한다. 회로를 보자면 아래와 같다.

전원회로

PCB에서 아날로그 회로에 노이즈가 타고가지 않도록 VDDA라고 설정했지만, 그냥 디지털만 사용한다면 VDD로 연결해도 무방하다.

그라운드도 잊지말자.

전원 핀마다 1개의 100nF 커패시터를 연결하고 추가적으로 탄탈 커패시터 10uF를 달아준다.

에도 전원을 공급해준다.

여기서 필자는 배터리를 사용할 생각이 없다. 따라서 기존 VDD를 연결한다.

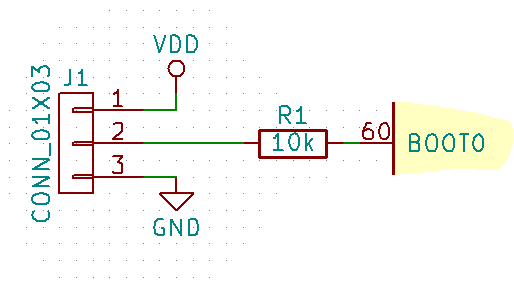

BOOT회로

별거 없다. 위처럼 3핀 커넥터를 달아서 사용자가 원하게 설정해주면 된다. BOOT0가 Low일 경우가 일반적이고 High일 경우는 시스템 붓로더에 접근할 경우로, 보통 양산할 때 유용하다. 이에 대한 자세한 내용은 데이터시트를 참고하면 된다.

선택해서 한다는게 이해하기 조금 어렵다면 이 제품을 참고하면 된다. 저 핀의 윗단에 금속이 있어 2핀을 연결하면 서로 전류가 통한다 .

BOOT1도 위와 같이 꾸민다. 보통 BOOT0가 LOW면, BOOT1은 DON’T CARE이므로, 굳이 서술하지 않는다.

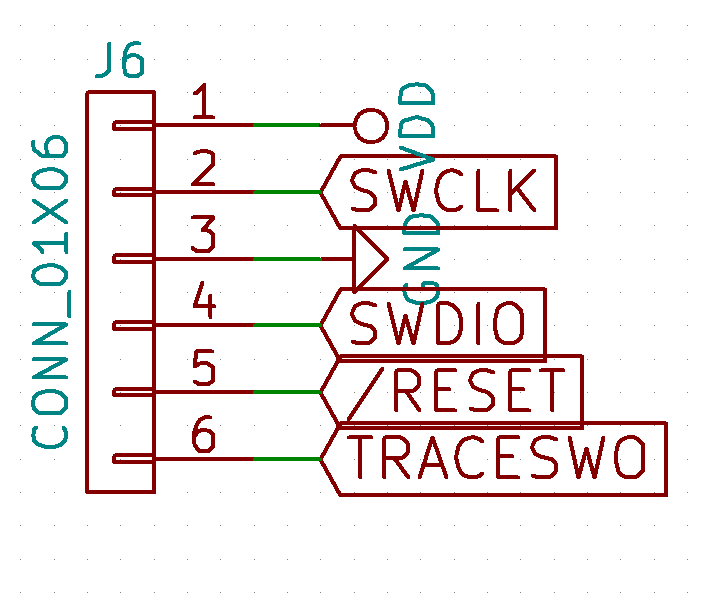

DEBUG회로

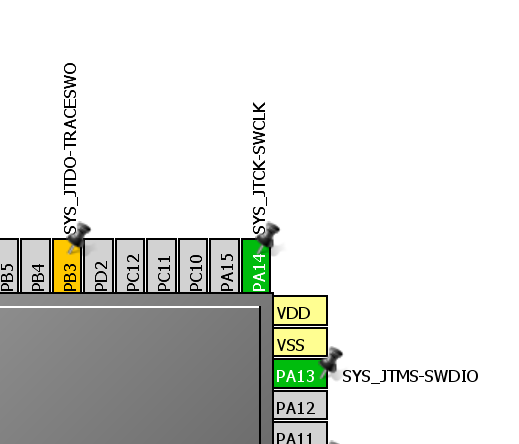

디버깅 툴로 ST-LINK V2-1을 사용한다고 가정하고 서술한다. ST-LINK V2-1회로를 찾아보면 SWD방식과 J TAG를 사용하는 방법이 있지만, 뉴클레오 보드를 보면 SWD방식으로 구성을 해놓았길래 SWD 방식을 채택했다. 핀은 총 6핀으로 전원핀 2개, 리셋 1핀, 디버깅 핀 3개로 구성했다. 여기서 TRACESWO핀은 그래프로 데이터를 보고 싶을 경우로 사용하는데, 보고 싶지 않다면 연결 안해도 동작한다.

여기서 필수적인 핀은 SWCLK, SWDIO이다. 리셋부는 구성 안해도 동작한다.

그래도 디버거가 RESET 신호를 줄 수 있도록 하는 것이 좋아 보여서 구성했다.

핀 세개는 위를 참고하시라.

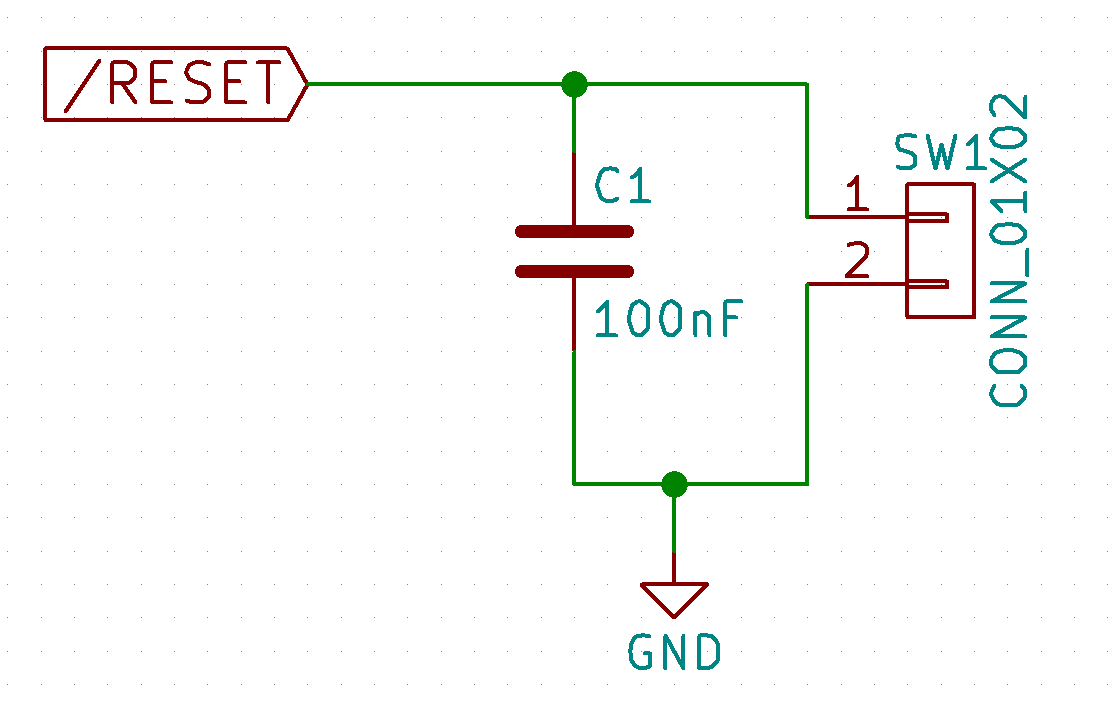

RESET회로

리셋 회로는 데이터시트에 있는 대로 구성했다. 내부적으로 풀업이 되어있어서 High 상태를 유지하다 스위치를 누르면 Low로 내려가는 식이다. 원래대로라면 Switch기호를 부착해야 하지만, KICAD는 이상하게 스위치 기호가 없길래 CONN기호를 사용했다. 어차피 부품 선택만 잘 해주면 이상 없다.

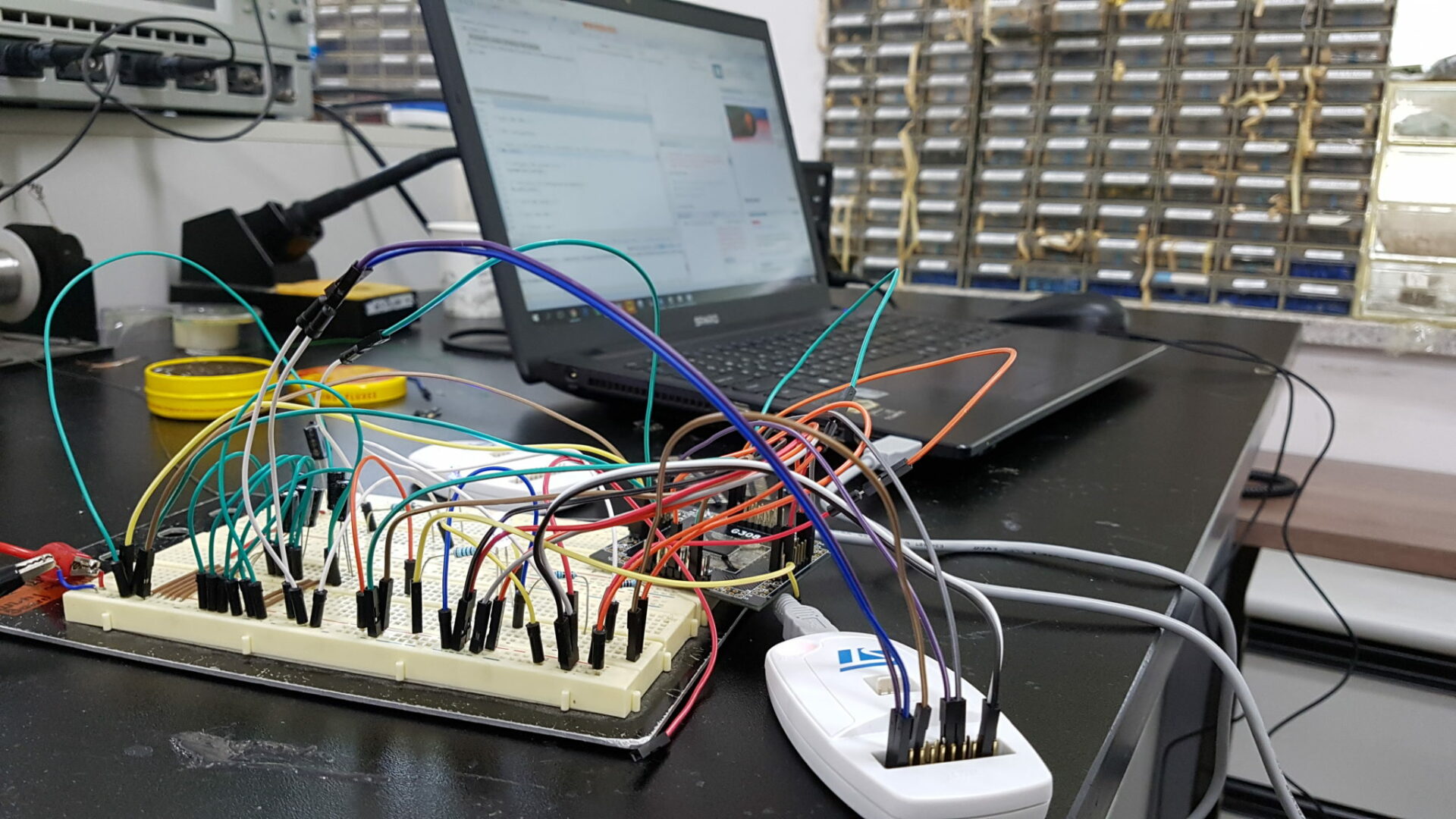

빵판으로 구성한 회로. 여기서 GPIO핀 하나 따서 LED를 구동시키니 잘 동작했다.

PCB도 잘 된다.