서론은 생략한다. 또한 필자는 64핀의 F103을 사용할 것 므로, 100핀 이상의 문서 기술은 생략한다. 리셋부도 딱히 필요 없어서 대다수가 생략됨.

1. POWER

- ADC 정확도를 높이기 위해 별도의 V_{DDA}핀이 있음

- ADC 전용 Ground Pin(V_{SSA})이 있음. Package에 따라 다르지만, V_{REF-}은 반드시 V_{SSA}핀과 연결되어 있어야 함.

PACKAGE가 64핀, 혹은 그 이하일 때.

V_{REF+}와 V_{REF-}핀 없음. 내부적으로 V_{DDA}와 V_{SSA}핀에 연결되어 있음.

Voltage Regulator

Voltage Regulator는 항상 Reset 후에 동작함. 아래와 같이 3가지 모드가 존재한다.

- Run Mode (동작 모드) : 모든 곳에 1.8V로 전원을 공급한다. (코어, 메모리, 주변 디지털 회로 등등)

- Stop Mode (정지 모드 ) : 내용 저장을 위해 레지스터와 SRAM에만 전원을 공급한다.

- Standby Mode(대기 모드) : regulator 동작 안함. 레지스터와 SRAM에 저장된 백업 영역과 대기 회로를 제외한 모든 데이터가 손실된다.

Power Supply

회로는 안정화된 V_{DD}에 의해 전원 공급을 받는다.

- 주의:

- ADC 사용 시 V_{DD}는 2.4V ~ 3.6V 사이 값을 가진다.

- ADC 미사용 시 V_{DD}는 2.0V ~ 3.6V 사이 값을 가진다.

- V_{DD}핀은 반드시 추가 디커플링 커패시터를 사용해야 함. 두 가지를 구현해야 한다.

- 핀마다 100nF 세라믹 커패시터를 사용한다.

- 대용량 세라믹 또는 탄탈 커패시터를 하나만 사용한다. 용량은 최소 4.7\mu F이지만, 보통 10\mu F를 사용한다.

- V_{BAT}핀은 1.8V~3.6V 전압을 사용하는 추가 배터리를 연결한다. 배터리를 안쓸거면 V_{DD}핀처럼 100nF 디커플링 세라믹 커패시터를 연결한다.

- V_{DDA}핀은 반드시 두 개의 디커플링 커패시터가 필요하다. 하나의 100nF 세라픽 커패시터와 하나의 1\mu F 탄탈 또는 세라믹 커패시터를 연결한다.

- 다음과 같은 추가 대책은 Analog 노이즈를 줄일 수 있다.

- V_{DD}에서 페라이트 비드를 추가해 V_{DDA}에 연결한다.

Figure 2. Power Supply Scheme

N은 V_{DD}와 V_{SS}의 갯수이다.

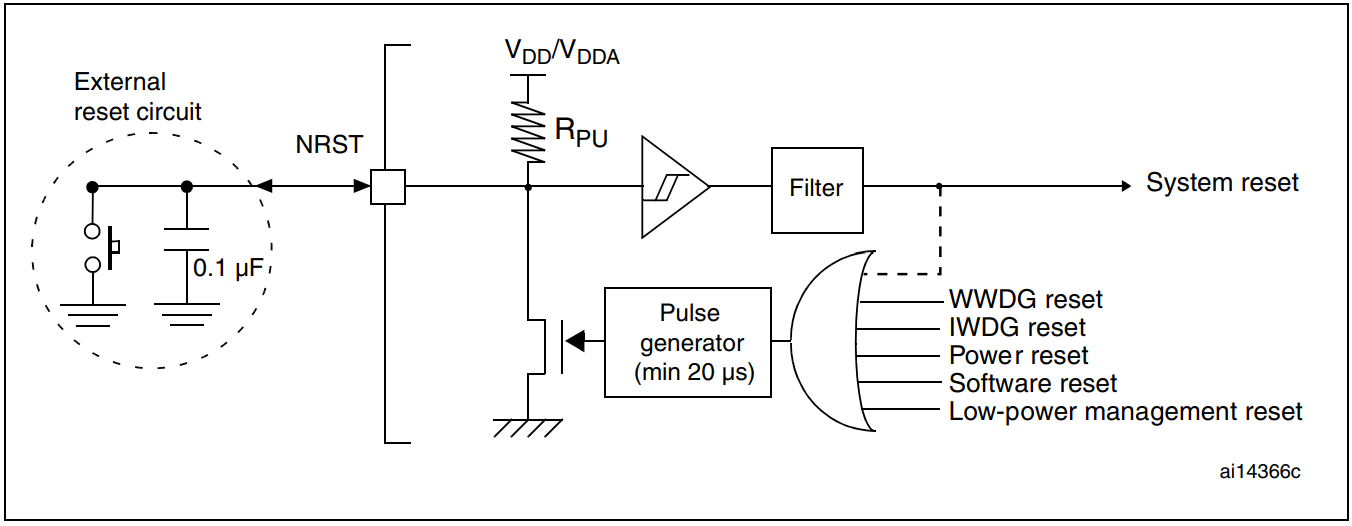

System Reset

NRST 핀이 low level(ground에 가까운 값을 가짐)이 되면 리셋이 된다.

Figure 5. Reset Circuit

풀-다운 커패시터가 충,방전 됨에 따라 장치 전력 소모가 증가한다. 커패시터 권장 용량은 100nF이나, 전력 소모를 제한하기 위해 10nF로 줄일 수 있다.